Генератор серий синхроимпульсов

Работа любой ЭВМ и любого цифрового устройства сопровождается передачей данных по тракту их обработки от предыдущих функциональных блоков и узлов к последующим. Взаимодействие этих блоков и узлов во времени организуется различными способами, рассмотренными в (1). Особо важную роль среди способов организации взаимодействия частей цифровых устройств и ЭВМ во времени играет синхронизация, осуществляемая с помощью специальных устройств синхронизации (синхронизаторов), сигналы от которых распределяются по всем частям ЭВМ. Эти сигналы разрешают прием и выдачу данных, а также тактируют процесс их обработки. Существуют однофазные и многофазные системы синхронизации. Многофазная синхронизация характеризуется наличием более чем двух серий (наборов) синхроимпульсов и применяется для увеличения быстродействия тактируемых устройств. Это осуществляется с помощью разбиения периода следования синхросигналов на несколько частей и использования в отдельных блоках ЭВМ или других цифровых устройств синхросигналов более высокой, чем основная, частоты. В данном случае необходимо разработать устройство синхронизации аналогичного назначения, формирующее четыре серии синхроимпульсов в соответствии с исходным ТЗ.

1. РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВА И ОБОСНОВАНИЕ ПРИНЯТЫХ РЕШЕНИЙ

1.1. Выбор и обоснование структурной схемы

Генератор может быть построен на основании четырехразрядного кольцевого счетчика и неполного линейного дешифратора, который можно реализовать на логических элементах, выполняющих функцию 2И.

Структурная схема генератора приведена на рис.1.1.

Рис. 1.1.Структурная схема генератора

СИ – тактовые синхроимпульсы

CT – кольцевой счетчик

DC – дешифратор

1.2. Разработка функциональных схем отдельных блоков устройства

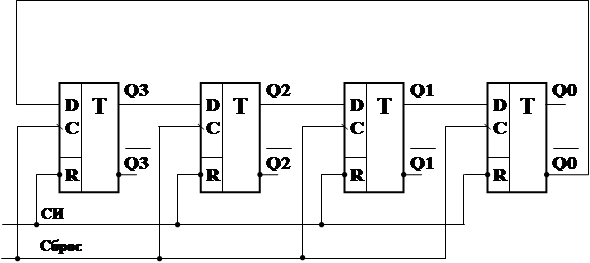

На рис.1.2 приведена функциональная схема кольцевого счетчика, построенного на основе обычного сдвигового регистра со сдвигом вправо. В качестве разрядных триггеров использованы D – триггеры с прямым динамическим управлением. Благодаря тому, что триггеры имеют как прямой ( Q ), так и инверсный ( Q ) выход, на входе схемы дешифратора, подключенного к прямым и инверсным выходам счетчика, нет необходимости использовать дополнительные инверторы для получения парафазных кодов. Таблица состояний и временная диаграмма работы счетчика приведены соответственно в табл.1.1 и на рис.1.5.

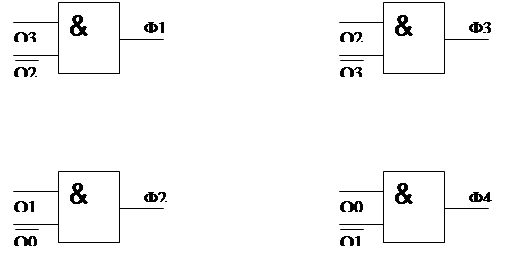

На рис.1.3 приведена функциональная схема дешифратора, который представляет собой простой неполный линейный дешифратор. Работа дешифратора в статическом режиме полностью описывается с помощью таблицы состояний ( табл.1.1 ). Согласно этой таблице функциональная схема может быть реализована на основе следующих логических выражений:

Q1 = Q3 Ù Q2 (1)

Q2 = Q1 Ù Q0 (2)

Q3 = Q2 Ù Q3 (3)

Q4 = Q0 Ù Q1 (4)

Для реализации данных логических выражений достаточно воспользоваться четырьмя элементами, реализующих функцию 2И.

1.3 Алгоритм и временная диаграмма работы генератора и отдельных блоков

Временная диаграмма, иллюстрирующая работу как генератора в целом, так и его отдельных блоков, приведена рис. 1.3.

Таблица 1.1.

Таблица состояний счетчика

СИ | ВЫХОДЫ | |||

Q3 | Q2 | Q1 | Q0 | |

0 1 2 3 4 5 6 7 8 | 0 1 1 1 1 0 0 0 0 | 0 0 1 1 1 1 0 0 0 | 0 0 0 1 1 1 1 0 0 | 0 0 0 0 1 1 1 1 0 |

Таблица 1.1.

Таблица состояний счетчика

ВХОДЫ | ВЫХОДЫ | ||||||

Q3 | Q2 | Q1 | Q0 | Ф1 | Ф2 | Ф3 | Ф4 |

0 1 1 1 1 0 0 0 0 | 0 0 1 1 1 1 0 0 0 | 0 0 0 1 1 1 1 0 0 | 0 0 0 0 1 1 1 1 0 | 0 1 0 0 0 0 0 0 0 | 0 0 0 1 0 0 0 0 0 | 0 0 0 0 0 1 0 0 0 | 0 0 0 0 0 0 0 1 0 |

Рис 1.2. Функциональная схема счетчика

Рис 1.3. Функциональная схема дешифратора

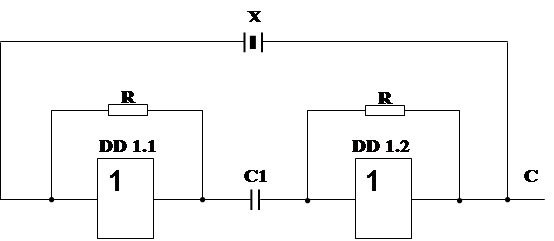

Функциональная схема задающего генератора ( G ) приведена на рис.1.4.

Рис 1.4. Функциональная схема генератора

1.4. Описание принципа действия

Так как после включения питания триггеры счетчика могут установиться в любое состояние ( ’’0’’ или ’’1’’), то перед началом работы необходимо установить все разрядные триггеры в нулевое состояние. Для этого на все входы установки в ''0'' разрядных триггеров ( R ) необходимо подать на короткое время сигнал низкого уровня, т.к. предложенные в задании триггеры имеют инверсный асинхронный вход установки в ''0''.

Длительность этого сигнала должна быть не меньше времени установки в ''0'' разрядных триггеров. Первый тактовый синхроимпульс, следующий после окончания сигнала ''сброс'', вызывает появление на выходе генератора первого фазового импульса Q1.

Работа генератора в статическом режиме полностью описывается таблицами состояний счетчика (табл. 1.1) и дешифратора (табл. 1.2). В динамическом режиме работа генератора осуществляется в соответствии с временной диаграммой, приведенной на рис. 1.5. Из этой временной диаграммы видно, что появляющийся на выходе дешифратора последовательно во времени импульсы управления с четырехфазным шаговым двигателем Ф1, Ф2, Ф3 и Ф4 соответствуют временной диаграмме задания. Период следования и длительность импульсов Ф1, Ф2, Ф3, Ф4 определяются частотой следования тактовых синхроимпульсов (СИ), поступающих от внешнего тактового генератора

Рис 1.5. Временная диаграмма работы генератора и его отдельных блоков

2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ

На основании структурной схемы генератора импульсных последовательностей, приведенной на рис. 1.1, а также функциональных схем отдельных блоков, разработанных в разд. 1.2, разработана принципиальная схема устройства, приведенная на черт. XXXXXXX.098033.010 Э3.

Генератор тактовых импульсов построен на двух инверторах DD1.1 и DD1.2, охваченных цепью положительной обратной связи. Стабильность частоты генерируемых прямоугольных импульсов обеспечивается за счет кварцевого резонатора XT,включенного в цепь положительной обратной связи по постоянному току между двумя инверторами DD1.1 и DD1.2. Резисторы R1 и R2 предназначены для смещения рабочей точки на амплитудно – передаточных характеристиках (АПХ) инверторов DD1.1 и DD1.2 на границу линейной области.

Для построения кольцевого счетчика на основе сдвигового регистра использована интегральная микросхема (ИМС) DD2 типа 1533 ТМ8, содержащая четыре D – триггера с прямым динамическим управлением, общими цепями синхронизации (С) и установки в ноль (R). Внешним монтажом все разрядные триггеры соединены последовательно друг с другом.

Инвертор DD1.3 предназначен для создания синхровхода счетчика с обратным динамическим управлением. Для построения неполного дешифратора с выходами Ф1, Ф2, Ф3 и Ф4 использована ИМС DD3 типа 1533 ЛИ1, содержащая четыре логических элемента, реализующих функцию 2И.

Выбор любой из четырех серий синхроимпульсов Ф1, Ф2, Ф3 или Ф4 осуществляется с помощью мультиплексора размерностью 4 ® 1, реализованного в микросхеме DD4.1 типа 1533 ИП2.

Выбор любого из четырех входных направлений 01, 02, 03 или 04 осуществляется с помощью двухразрядного адресного кода, подаваемого на соответствующие входы А1 и А2 мультиплексора. В ИМС 1533 КП2 содержится два идентичных мультиплексора с общими адресными входами. Выбор необходимого MUX осуществляется с помощью разрешающих входов Е0 и Е1 (Enable). Для этого на вход Е0 подан сигнал логического нуля.

3. Расчет основных параметров и характеристик

3.1. Расчет временных характеристик

Основная задача этого раздела – определение допустимых значений временных характеристик (минимальная длительность импульса) входных сигналов и как следствие, значений параметров, характеризующих быстродействие всего устройства в целом.

Составим таблицу, характеризующую параметры микросхем.

3.2. Расчет надежности

Интенсивность отказов l характеризуется отношением числа отказавших изделий в единицу времени к числу изделий, продолжающих оставаться исправными к началу рассматриваемого промежутка времени:

l = m/Nt , (3.1)

где m – число изделий, отказавших за время t,

N – число исправно работающих изделий к началу промежутка времени.

Если предположить, что отказы различных элементов взаимно независимы и каждый отказ носит катастрофический характер, т.е. полностью нарушает работоспособность, то интенсивность отказов устройства равна сумме интенсивностей отказов элементов составляющих устройство.

, (3.2)

где li – интенсивность отказов элементов i-го типа;

Сi – количество элементов i-го типа, входящих в устройство.

Наработка на отказ равна:

Т = 1/l (3.3)

Интенсивность отказа элементов следующая:

Микросхемы 1533й серии 0,85 * 10-6 (1/ч);

Резисторы 0,9 * 10-6 (1/ч);

Тогда,

l = (17·0,85+2·0,9)·10-6 = 16,25 · 10-6 1/ч,

Т = 1/16,25 ·10-6 = 0,062 ·10-6 = 6,2 · 10-4 (ч).

| Обозначение | Наименование | Количество |

Конденсаторы | ||

| С1 | КМ – 6 – 9 - 0,47 +- 10% ОЖО 464. 023 ТУ | 1 |

| С2 | К73 – 9 - 10 ОЖО 468. 030 ТУ | 1 |

| С3, С4 | КМ – 6 – 9 - 0,068 +- 10% ОЖО 464. 023 ТУ | 2 |

Резисторы | ||

| R1, R2 | МЛТ – 0,125 – 100 кОм +- 10% | 2 |

Микросхемы | ||

| DD1, DD3 | КР1533 ЛН1 | 2 |

| DD2 | КР 1533 ТМ8 | 1 |

| DD4 | КР 1533 ЛП2 | 1 |

Кварц | ||

| XT | РВ – 72 – 20 МГц ТУ 18 – 780 - 780 | 1 |

4. МОДЕЛИРОВАНИЕ УСТРОЙСТВА

4.1. Моделирование генератора

Моделирование устройства осуществлялось с использовани- ем пакета прикладных программ '' Electronics Workbench '' 4.0 (EWB 4.0). Была продемонстрирована работа основных блоков устройства – счетчика и дешифратора. Тактовые синхроимпульсы на С-вход счетчика подавались от внешнего генератора, имеющегося в библиотеке приборов пакета EWB 4.0.

Триггеры и логические элементы, необходимые для построения счетчика и дешифратора, были взяты из соответствующих библиотек элементов пакета EWB 4.0. В связи с тем, что моделирование осуществлялось на основе функциональных схем, разработанных в разд. 1.2, библиотеки интегральных микросхем пакета EWB 4.0 не использовались.

Контроль необходимых сигналов в соответствии с временной диаграммой, разработанной в разд. 1.3, осуществлялся с помощью восьмиканального логического анализатора из библиотеки приборов пакета EWB 4.0.

Результаты, полученные в процессе работы на логическом анализаторе совпадают с результатами, представленными на временной диаграмме работы генератора и отдельных его блоков.