Видеопамять

В растровых дисплейных системах видеопамять организована в виде прямоугольного массива точек. Элемент видеопамяти, стоящий на пересечении конкретных строки и столбца видеопамяти, хранит значение яркости и/или цвета соответствующей точки. Отображаемая на экране часть видеопамяти называется экранным буфером (буфером регенерации или экранной битовой картой). Регенерация изображения осуществляется последовательным построчным сканированием экранного буфера.

Так как каждый элемент видеопамяти определяет один элемент отображения размером в точку на экране монитора, то каждая точка экран (и соответствующий ей элемент видеопамяти) обозначаются термином пиксел (pixel - picture element).

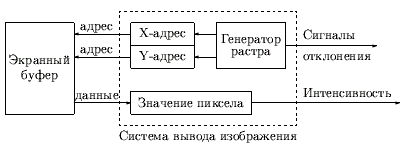

Задача системы вывода изображений (видеоконтроллера) состоит в циклическом построчном просмотре экранного буфера от 25 до 100 раз в секунду. Адреса видеопамяти генерируются синхронно с координатами растра и содержимое выбранных пикселов используется для управления цветом и интенсивностью луча. Общая организация системы вывода изображений приведена на рис.1.

Рис.1. Экранный буфер и система вывода изображения

Генератор растровой развертки формирует сигналы отклонения и управляет адресными X и Y регистрами, определяющими следующий элемент буфера регенерации.

В идеальном случае время, требуемое для регенерации экранного буфера, должно быть много меньше, чем время, необходимое для манипуляций с данными, что позволит быстро обновлять или двигать изображение. Это означает, что усилители отклонения и усилитель, управляющий интенсивностью луча, должны быть очень широкополосными, чтобы обеспечить требуемую скорость передачи данных между экранным буфером и системой вывода изображения.

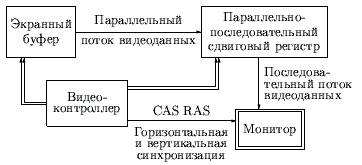

Частота регенерации для графических дисплейных систем среднего разрешения лежит в пределах 50 Мгц, а для систем высокого разрешения достигает 100-125 Мгц, с явной тенденцией к частотам более 125 Мгц в последнее время. При таких частотах таймирование регенерации экранного буфера становится важной задачей при проектировании подсистемы графического вывода. Так ка обычная DRAM память не обеспечивает времени доступа, подходящего для существующих мониторов высокого разрешения, то регенерация видеопамяти на таких частотах требует ее специальной организации. Пример организации видеопамяти, построенной на обычной динамической памяти с произвольным доступом (DRAM) приведен на рис. 2.

Рис. 2. Регенерация экранного буфера, построенного на обычной динамической памяти (DRAM)

В такой системе регенерация экранного буфера видеопамяти осуществляется с помощью параллельно-последовательного преобразования. Выполняя регенерацию, видеоконтроллер выставляет адрес слова, требуемое слово данных видеопамяти (обычно 16-32-64 бита) затем трансформируется в последовательный видеопоток (videostream) с помощью внешнего сдвигового регистра под контролем аппаратуры регенерации. На рис.2 показана реализация регенерации экранного буфера для системы с одним слоем. Системы регенерации со многими слоями требуют такого же количества (16-32-64) битовых слов, подлежащих регенерации и параллельно-последовательных сдвиговых регистров, что и число битовых слоев видеопамяти.

Если частота регенерации экранного буфера составляет порядка 100 Мгц, то такое параллельно-последовательное преобразование уменьшает требования к частоте тактирования параллельно считываемого слова из экранного буфера видеопамяти до 6.25 Мгц, что требует времени доступа порядка 160 нс. При такой организации видеопамяти манипуляции с данными и обновление экрана должны происходить во времена межстрочного и межкадрового интервалов, когда регенерации не происходит. Таким образом, узкое место для обычной DRAM памяти в качестве видеопамяти в графических дисплейных системах вытекает из двух противоречивых требований:

для растровых дисплейных систем должна осуществляться постоянная регенерация экранного буфера видеопамяти, что требует считывания выводимой на экран монитора графической информации с периодическим, жестко заданным циклом;

с другой стороны, требуется время для обновления больших массивов данных видеопамяти со стороны собственно аппаратуры генерации изображений, работающей, как правило, в цикле чтение-модификация-запись.

Доступные в настоящее время DRAM устройства даже с наиболее быстрыми режимами доступа не обеспечивают быстрого чтения их содержимого для поддержки требуемого ритма регенерации, оставляя крайне мало времени графическому процессору для модификации изображения. Таким образом, ограниченная полоса пропускания DRAM памяти ограничивает доступ аппаратуры формирования изображений к данным видеопамяти на время значительных периодов регенерации экранного буфера. Проблема усложняется по мере увеличения экранного буфера из-за возрастания числа отображаемых пикселов для мониторов высокого разрешения или при увеличении числа битов на пиксел в системах с большим количеством отображаемых цветов.

Для решения этой проблемы разработаны различные архитектуры видеопамяти, включая двухпортовую видеопамять, двойное буферирование и др.

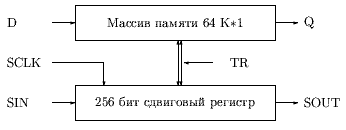

Однако лучшее решение этой проблемы достигается за счет применения нового типа DRAM памяти, получившей название VRAM (Video Random Accses Memory), например. Texas Instrument 4161, разработанной специально для использования в качестве памяти изображения в растровых дисплейных система. Структурная схема подобной памяти приведена на рис.3.

Рис. 3. Структурная схема VRAM памяти

Эта видеопамять содержит 2 порта, обеспечивая независимый доступ со стороны видеоконтроллера для регенерации и аппаратуры формирования изображений - графических процессоров. VRAM фактически представляет собой обычную DRAM память, которая была "внутренне" модифицирована посредством добавления сдвигового регистра. D и Q - это обычные входы и выходы порта с произвольной выборкой. Сигнал TR активируется на время передачи данных между сдвиговым регистром и видеопамятью. Сигналы SIN и SOUT - последовательные вход и выход сдвигового регистра, а сигнал SCLK - последовательный вход, управляющий сдвиговым регистром. Сдвиговый регистр загружается параллельным потоком в 256 бит из массива памяти за один цикл регенерации экрана. Длительность этого цикла не длиннее, чем стандартный цикл памяти. Обычно сдвиговый регистр загружается 1 раз во время обратного хода луча. Когда обратный ход заканчивается, на вход SCLK подается сигнал, вызывая сдвиг данных на последовательном выходе SOUT.

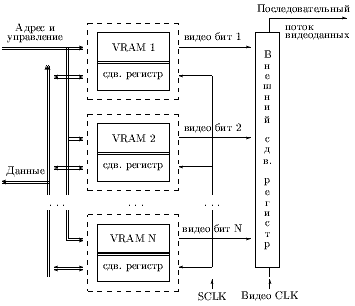

На рис.3 показан модуль видеопамяти объемом 64 Кбайт. Видеопамять объемом 256 Кбайт может быть построена из 4 модулей по 64 Кбайт (рис.4).

Рис. 4. Структурная схема многослойной VRAM памяти

В этом случае выходы SOUT от нескольких VRAM модулей подаются на параллельные входы внешнего сдвигового регистра, последовательный выход (CLK) которого тактируется со скоростью вывода точек (видеопотока битов), требуемой для регенерации экрана монитора.

В видеопамяти с такой организацией время на регенерацию экранного буфера (отображения на экран монитора) составляет менее 1.5% времени доступа. В системах же с обычной DRAM памятью время на регенерацию экрана составляет от 40% до 60% времени доступа.

Таким образом, применение VRAM обеспечивает практически полное время доступа для модификации данных видеопамяти, так как на одну строку сканирования растра требуется одна загрузка сдвигового регистра. Следовательно, в то время как предварительно загруженные видеоданные "выталкиваются" из сдвигового регистра в канал графического вывода, одновременно может осуществляться произвольный доступ к видеопамяти со стороны графических процессоров для модификации изображения.

ПРИНЦИПЫ ОРГАНИЗАЦИИ ВВОДА / ВЫВОДА

ИНФОРМАЦИИ В МИКРОЭВМ

Вводом/выводом (ВВ) называют передачу данных между ядром ЭВМ, включающим в себя процессор и ОП, и периферийными устройствами (ПУ).

Система ВВ – это единственное средство общения ЭВМ с внешним миром. Ее возможности в серийных ЭВМ представляют собой один из важнейших параметров, определяющих выбор машины для конкретного применения.

Несмотря на разнообразие ПУ, в настоящее время разработано несколько стандартных способов их подключения к ЭВМ и программирования ВВ. Существует три режима ВВ:

· Программный ВВ (нефорсированный).

· ВВ по прерыванию (форсированный).

· Прямой доступ к памяти (ПДП).

Реализация ВВ в каждом из этих режимов отличается программно-аппаратными затратами и, самое важное, скоростью выполнения операций обмена и непроизводительными затратами времени процессора. Суть каждого из трех режимов состоит в следующем.

Программный ВВ. Инициирование и управление ВВ осуществляет процессор по командам прикладной программы. ПУ играют пассивную роль и только сигнализируют о своем состоянии, в частности о готовности к операциям ВВ.

ВВ по прерыванию. Операции ВВ инициирует ПУ, генерируя сигнал запроса прерывания, при этом процессор переключается на подпрограмму обслуживания данного ПУ, вызвавшего прерывание. В результате выполнения подпрограммы (обработчика) осуществляется обмен данными. Действия, выполняемые обработчиком, определяются пользователем, а непосредственно операциями ВВ управляет процессор.

Таким образом, как при программном ВВ, так и при ВВ по прерываниям операциями обмена управляет процессор, поэтому очень часто эти два варианта обмена не разделяют и рассматривают их как программный ВВ. В англоязычной литературе – Programmed Input/Output (PIO). Однако в настоящем курсе эти варианты обмена рассматриваются отдельно.

Прямой доступ к памяти. Процессор в передаче данных не участвует. Он отключается от системной магистрали, а все операции обмена данными идут под управлением специального управляющего устройства – контроллера ПДП. Этот режим используется для быстродействующих ПУ, когда пропускной способности процессора недостаточно.

Следует отметить, что общие принципы организации систем прерывания уже рассмотрены в гл. 6. Организация систем ПДП подробно рассмотрена в гл. 11. Ниже рассматривается простейший случай организации радиальных систем прерывания и ПДП для микроЭВМ на базе МП КР580, поэтому материал настоящего раздела частично перекрывается с материалом, изложенным в гл. 6 и в гл. 11.