Технология описания аппаратуры

Технология описания аппаратуры – это метод однозначного описания межэлементных соединений и работы электрической и электронной частей аппаратных средств вычислительной техники.

Технология опирается на применение Hardware Description Language (HDL) – языков описания аппаратуры. Написание HDL-кода вместо использования схемотехнических компонентов (например, логических вентилей) является в настоящее время основным направлением в области проектирования цифровых систем.

Сегодня широкое распространение в рамках представленной технологии получили такие высокоуровневые языки как VHDL, Verilog, Schematik и некоторые другие. Среди перечисленных языков описания аппаратуры наиболее универсальным является VHDL.

Общая технология использования языков HDL предполагает, что:

- проектируемое устройство иерархически разбивается на составные части (компоненты);

- каждый компонент имеет четко очерченный интерфейс (для его соединения с другими компонентами) и точное функциональное описание для моделирования его поведения;

- функциональное описание может быть основано либо на структуре, либо на алгоритме, которыми определяется функционирование данного компонента.

Внутренняя структура компонента может быть скрыта от проектировщика по принципу «черного ящика». В определенных случаях абсолютно не нужно знать, как структурирован компонент. Разработчика обычно интересуют лишь входы и выходы компонента, спецификация его функций и время доступа. В качестве «черных ящиков» традиционно используют программируемые интегральные схемы – ПЛИС (FPGAs, СPLDs).

Описание компонента состоит из двух частей:

- описания интерфейса («сущность»), которое описывает взаимосвязи между компонентом и средой его «обитания» (функционирования);

- архитектуры (архитектурное тело), описывающей поведение компонента с функциональной или структурной точки зрения относительно входов и выходов.

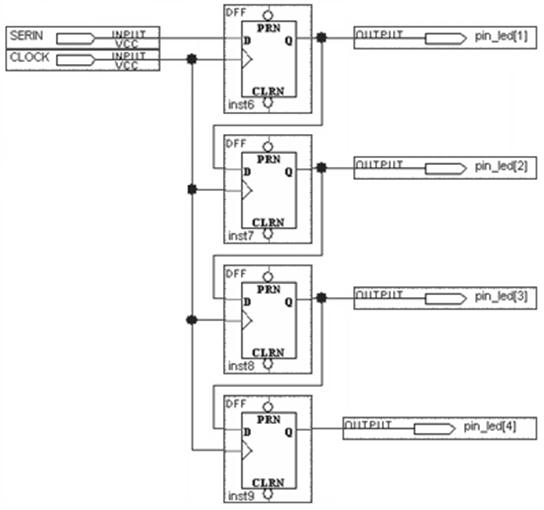

Возможные варианты реализации модели сдвигового регистра по данной схеме на языках Schematik, VHDL и Verilog представлены ниже на рисунках (а), (б) и (в) соответственно.

а) описание сдвигового регистра на языке Schematik

library ieee;

use ieee.std_logic_1164.all;