ШИМ регулятор на ИС TL494

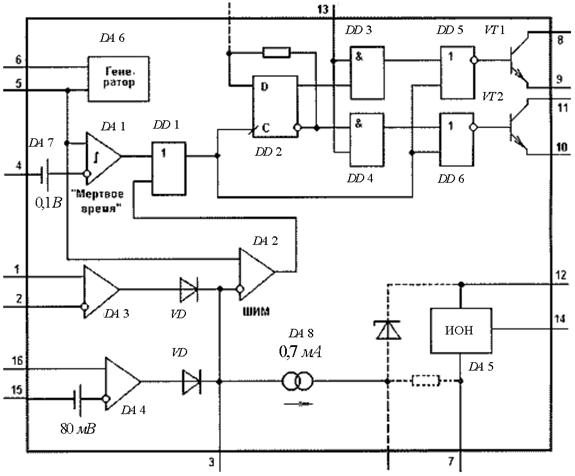

Рис. 96

Рис.97

Буферный усилитель DA3 своими входами - вход 3 и вход 4 - подключается к выходной точке канала вторичного напряжения. Вместе с функциямибуферизации этот усилитель нормирует уровень регулируемого напряжения, то есть выполняет функции делителя напряжения, для возможности сопоставления его величины с номиналом источника опорного напряжения. Сравнение этих значений напряжения и выработка сигнала рассогласования производится усилителем DA2. Сигнал рассогласования через диод развязки VD2 подается на один из входов компаратора DA4. На второй вход компаратора поступает пилообразное напряжение, сформированное каскадом ФПН. Запуск каскада ФПН (начало линейного нарастания напряжения) и одновременный сброс процесса предыдущего периода происходит в момент прихода на него фронта импульса, вырабатываемого генератором. Генератор вырабатывает последовательность импульсов с относительно стабильными частотными характеристиками. Этим заканчивается работа ШИМ регулятора на уровне обработки аналоговых сигналов. Дальнейшее формирование ШИМ сигнала происходит цифровыми способами, при которых все активные элементы, включая и дискретные из КС, функционируют в ключевых режимах.

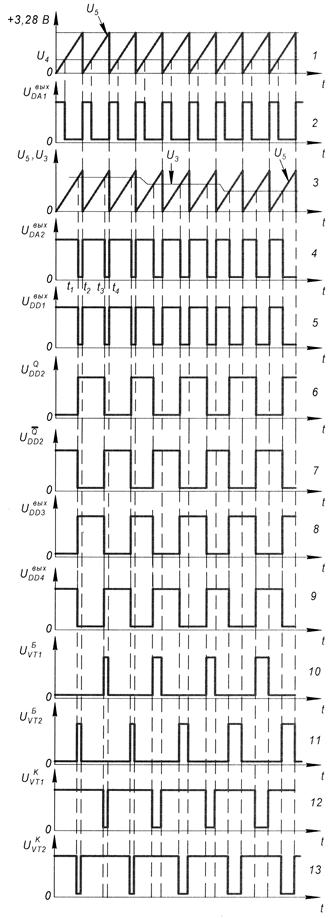

После отработки компаратором DA4 входных воздействий на его выходе появляется последовательность импульсов, синхронных с частотой пилообразного напряжения, но с модулированной длительностью самого импульса - цифровой ШИМ сигнал. Эта последовательность поступает на входы цифровых элементов DD2.1, DD2.2, выполняющих логическую функцию И (схема совпадения по высокому логическому уровню). На второй вход каждого из элементов схемы DD2 подается последовательность импульсов, частота которых в два раза ниже исходных, формируемых генератором. Понижение частоты в два раза происходит на элементе DD1 - D-триггере, включенном в режиме деления исходной частоты. Изменение состояния выходов триггера происходит при поступлении на его счетный вход С фронта импульса, формируемого генератором. На выходах триггера Q (прямой выход) и -Q (инверсный выход) в каждый момент времени сигналы противофазны. В моменты совпадения высоких уровней сигналов от компаратора и сигналов от делителя частоты (триггера) на входах элементов DD2 и на их выходах появляются импульсы высокого уровня. Периодичность импульсов на выходе каждого из элементов DD2 совпадает с периодом исходной частоты генератора деленной на два. Графически процесс работы ШИМ регулятора показан в виде диаграмм на рис. 97. Точки на схеме (рис. 97), для которых приведены эпюры напряжений, отмечены цифрами в кружочках. Для наглядности на второй диаграмме (рис. 97) кривые напряжений для точек 1 (пилообразное напряжение) и 2 (напряжение на выходе буферного усилителя DA1) совмещены.

Работа данного ШИМ регулятора осуществляется следующим образом: на каскад согласования КС от каждого из элементов схемы DD2 поступают две сдвинутые по времени последовательности импульсов. Это обусловлено спецификой построения силового каскада преобразователя напряжения. Длительность импульсов в каждой последовательности находится в обратно пропорциональной зависимости от текущей величины напряжения вторич-ной цепи (на нагрузке). Силовой каскад преобразователя находится в актив-ном состоянии (передачи энергии) в нагрузку в течение действия на него модулированных по длительности импульсов. Так происходит регулировка выходного напряжения для поддержания его уровня в заданных пределах.

Усилительный каскад DA1 предусмотрен для отключения (блокировки) схемы ШИМ регулятора во время резкого возрастания потребления тока в нагрузке. Входы схемы DA1 подключаются к датчику тока, установленному в цепи нагрузки. Пока разность потенциалов на входах DA1 не превышает заданной величины, то есть ток потребления нагрузки не выходит за верх-нюю допустимую границу, ШИМ регулятор работает в обычном режиме. В момент возрастания тока нагрузки выше установленного предела на выходе DA1 напряжение повышается до величины, достаточной для открывания диода VD1. На катоде VD1 создается положительное напряжение, закрываю-щее диод VD2. Сигнал рассогласования, поступающий от усилителя ошибки DA2 на вход компаратора DA4, шунтируется. Напряжение, установленное на входе компаратора, вызывает резкое сужение импульсов, поступающих от него на цифровые схемы DD2.1 и DD2.2. Силовая часть преобразователя переходит в защищенный режим работы, принудительно ограничивая уро-вень энергии, передаваемой на КС. ШИМ регулятор автоматически восстанавливает работоспособность после устранения перегрузки по выходу.

Интегральная микросхема управления TL494 двухтактным полумостовым импульсным преобразователем напряжения.

В современных источниках вторичного электропитания (ИВЭП) для формирования управляющего напряжения переключения мощных транзисторов преобразователя обычно используются специализированные интегральные микросхемы (ИМС в дальнейшем - ИС).

Идеальная управляющая ИС для обеспечения нормальной работы двухтактного преобразователя в режиме ШИМ должна удовлетворять большинству из перечисленных ниже условий [13]:

· рабочее напряжение не выше 40 В;

· наличие высокостабильного термостабилизированного источника опорного напряжения;

· наличие генератора пилообразного напряжения;

·  обеспечение возможности синхронизации внешним сигналом программируемого плавного запуска;

обеспечение возможности синхронизации внешним сигналом программируемого плавного запуска;

· наличие усилителя сигнала рассогласования

с высоким синфазным напряжением;

· наличие ШИМ-компаратора;

· наличие импульсного управляемого триггера;

· наличие двухканального предоконечного каскада с защитой от КЗ;

· наличие логики подавления двойного импульса;

· наличие средств коррекции симметрии выходных напряжений;

· наличие токоограничения в широком диапазоне синфазных напряжений, а также токоограничения в каждом периоде с отключением в аварийном режиме;

· наличие автоматического управления с прямой передачей;

· обеспечение отключения при понижении напряжения питания;

· обеспечение защиты от перенапряжений;

· обеспечение совместимости с ТТЛ/КМОП логикой;

· обеспечение дистанционного включения и отключения.

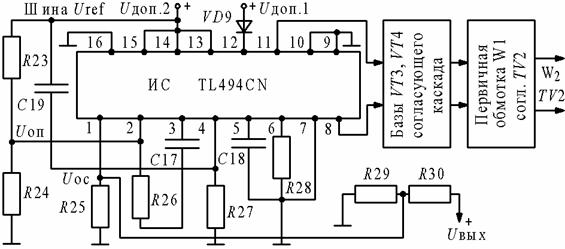

Все основные преобразования ШИМ сигналов, а также их формирование осуществляется модулятором, выполненным на микросхеме типа TL494. Существует два типа корпусов, в которых выпускается данная микросхема. В источниках питания, как правило, используется пластиковый корпус DIP, имеющий 16 выводов (рис. 98). Полное наименование микросхемы в таком корпусе - TL494CN. Обозначение относится к микросхеме производства фирмы Texas Instruments. Функциональное назначение выводов микросхемы приведено в табл. 7.

Таблица 7

| IN1 | Неинвертирующий (прямой +) вход усилителя ошибки 1 | |

| IN1 | Инвертирующий (-) вход усилителя ошибки 1 | |

| FB | Вход сигнала «обратной связи» | |

| DTC | Вход регулировки «мертвого времени» (время, в течение которого закрыты оба выходных транзистора, причем независимо от величины тока нагрузки) | |

| Ct | Вывод для подключения внешнего конденсатора ко встроенному генератору пилообразного напряжения | |

| Rt | Вывод для подключения внешнего резистора ко встроенному генератору пилообразного напряжения | |

| GND | Общий вывод питания | |

| C1 | Коллектор первого усилительного транзистора | |

| E1 | Эмиттер первого усилительного транзистора | |

| E2 | Эмиттер второго усилительного транзистора | |

| C2 | Коллектор второго усилительного транзистора | |

| Ucc | Общее положительное напряжение питания микросхемы | |

| OTC | Выбор режима работы - возможна работа ИС в одно- или двухтактном режиме: если на этом выводе присутствует логическая "1" (+2,4...+5 В), то транзисторы открываются поочередно (двухтактный режим работы); если на выводе будет "0" (0...0,4 В), то это однотактный режим | |

| Uref | Выход стабильного опорного напряжения (+5 В) | |

| IN2 | Инвертирующий (-) вход усилителя ошибки 2 | |

| IN2 | Неинвертирующий (прямой +) вход усилителя ошибки 2 |

Соответствующие аналоги этой микросхемы выпускают и некоторые другие фирмы, причем каждая из них присваивает свое фирменное обозначение. Приведем примеры: фирма FUJITSU - MB3759, фирма SAMSUNG-КА7500, фирма FAIRCHILD - ТА494, микросхема российского производства - КР1114ЕУ4, фирма SHARP - IP3MO2. Эта микросхема предназначена специально для построения ШИМ узлов. В корпусе микросхемы TL494CN заключены все необходимые каскады.

Функциональная схема интегрального ШИМ преобразователя типа TL494 изображена на рис. 99.

Рис. 99

Элементы, изображенные на функциональной схеме, имеют следующие наименования и назначение:

· на элементах, входящих в состав узла под общим названием «Генератор», собран основной каскад генератора пилообразного напряжения (ГПН), временные характеристики колебаний которого задаются внешними элементами Rt ,Сt, подключаемыми к выводам 5 и 6 DA6 , при этом частота генерации будет равна

f = 1,1 / (Rt × Ct)

· источник опорного напряжения (выв.14) предназначен для формирования стабильного напряжения с номинальным значением +5 В, используемого для работы каскадов сравнения и выработки напряжения ошибки. Точность источника опорного напряжения находится в пределах ±5%;

· элемент DA1 - компаратор «мертвой зоны», временного интервала между выходными импульсами;

· элемент DA2 - компаратор сравнения сигналов рассогласования и пилообразного напряжения - ШИМ компаратор;

· операционные усилители DA3 и DA4 – схемы выработки сигналов рассогласования;

· элементы с номерами DD1 - DD6 относятся к технике цифровой автоматики и выполняют логическую обработку сигнала, поступающего от ШИМ компаратора DA2;

· два транзистора VT1 и VT2 используются для построения усилителей уровня и мощности выходных импульсных последовательностей. Выводы коллекторов и эмиттеров этих транзисторов оставлены ненагруженными для расширения возможностей по их подключению к последующим каскадам;

· источник постоянного напряжения с номиналом 0,1 B DA7;

· источник постоянного тока с номиналом 0,7 мА DA8.

Операционные усилители сигнала ошибки имеют рабочий диапазон входных напряжений от -0,3 до 2 В. Последнее (наибольшее) значение соответствует Un - напряжению питания микросхемы. На входе компаратора «мертвой зоны» технологически установлено смещение, обеспечивающее гарантированное наличие минимальной паузы между импульсами управления. Рабочее напряжение питания на микросхеме в диапазоне от 7 до 40 В может быть установлено произвольным. Предельное значение напряжения питания микросхемы и уровень напряжения на коллекторах выходных транзисторов составляет 41В. Максимальное значение тока коллектора Iк max равно 250 мА, рекомендованный рабочий ток - 200 мА, рассеиваемая мощность 1Вт.

Рабочий диапазон частот генератора пилообразного напряжения составляет от 1 до 300 кГц. Конденсатор, подключаемый к выводу 5 микросхемы ИC, может иметь любое значение номинала от 470 пФ до 10 мкФ, резисторы для установки во времязадающей цепи - в пределах 1,8-500 кОм.

Температурный диапазон работы микросхемы типа TL494CN составляет 0-70 °С.

Преобразователь импульсов, действующий по принципу модуляции их ширины, является одним из основных каскадов импульсного источника питания. Принцип работы источника состоит в том, что от ШИМ регулятора зависит поступление всей энергии во вторичные цепи питания. Правильность же его работы определяют параметры стабилизации вторичных напряжений. Выше был описан (см. выше) общий принцип широтно-импульсной модуляции и его использование в импульсных источниках вторичного электропитания. В данном разделе будет рассмотрено практическое воплощение этого принципа на примере специального каскада, предназначенного для управления работой источника питания, например, в компьютерах. На фрагменте принципиальной схемы, приведенной на рис.100, непосредственно к каскаду ШИМ преобразователя относятся узлы, построенные на следующих активных элементах:

· микросхема ИC типа TL494 - ШИМ преобразователь. Цепи пассивных элементов, подключенные к микросхеме, задают динамические параметры ее работы, а также являются составными частями датчиков контроля уровней вторичных напряжений;

· группа элементов на транзисторах и согласующем трансформаторе ТV2 образует каскад согласования уровня и мощности импульсных сигналов между выходом ШИМ преобразователя и входными цепями усилителя мощности;

· узел на других транзисторах установлен для ШИМ регулятора с целью получения сигналов о неконтролируемом возрастании или понижении уровней вторичного напряжения; он используется также для защиты вторичных цепей.

С момента подачи напряжения питания на вывод 12 относительно вывода 7 ШИМ регулятор начинает формирование на выходных контактах (выводы коллекторов и эмиттеров транзисторов VT1 и VT2) импульсных сигналов. Формально для получения на этих выводах последовательностей импульсов никаких сигналов обратной связи не требуется. Но к микросхеме должны быть подключены пассивные элементы, задающие параметры работы генератора и обеспечивающие смещения на входах операционных усилителей. Для наблюдения импульсов на выводах выходных транзисторов в схеме должны быть установлены дополнительные нагрузочные резисторы, определяющие схему их включения.

Рассмотрим схему включения ШИМ преобразователя в системе управления импульсным источником питания, пользуясь обозначениями на функциональной (рис.99) и принципиальной (рис.100) схемах.

При подаче напряжения питания на вход импульсного источника вспомогательный источник, формирует два напряжения Uдоп1 и Uдоп2. Первое предназначено для запитки стабилизатора канала дежурного режима (если в этом есть необходимость), а второе для подачи питающего постоянного напряжения на микросхему ШИМ стабилизатора. Питание ШИМ преобразователя производится напряжением, гальванически развязанным от первичной сети питания.

постоянного напряжения на микросхему ШИМ стабилизатора. Питание ШИМ преобразователя производится напряжением, гальванически развязанным от первичной сети питания.

Рис.100

Напряжение, подаваемое на вывод 12 (рис.101) микросхемы ИC от выпрямителя на VD9, не стабилизированное и служит для начального запуска этой микросхемы. Для формирования пилообразного напряжения внутренним генератором микросхемы ИC между ее выводом 6 и общим проводом вторичного напряжения подключен резистор R28 с номинальным значением сопротивления, например, 12 кОм, а между общим проводом и выводом ИC 5 включен конденсатор С18 емкостью, например, 1500 пФ(рис.100). Согласно сервисной документации на микросхему TL494, расчет частоты генерации, применительно к элементам данной принципиальной схемы, может быть произведен по следующей формуле:

При указанных значениях элементов RC цепочки, частота работы генератора составляет ~55,5 кГц. Внутренний генератор формирует сигнал с нарастающим напряжением, форма которого представлена на верхней диаграмме рис.101.

Согласно данным технической документации на микросхему TL494, нарастание напряжения доходит до уровня +3,2 В, после чего конденсатор разряжается и пилообразное напряжение U5 на нем скачком падает до нулевого значения. Затем процесс циклически повторяется (см. диаграммы на рис. 101). Вид сигналов имеет качественный характер и не отражает реальных временных и амплитудных соотношений.

Пилообразное напряжение подается на инвертирующие входы компаратора «мертвой зоны» - элемент DA1 и ШИМ компаратора - элемента DA2, Ко второму входу компаратора подключен, внутренний источник начального смещения, величина которого задана и составляет U4=100 мВ.

Рис. 101

На диаграмме 1 рис. 101 наличие этого источника условно изображено прямой линией, пересекающей «зубцы» пилообразного напряжения. Компаратор является пороговым устройством, поэтому на его выходе формируется сигнал, значения которого принимают только два состояния. Если на инвертирующем входе напряжение превышает уровень напряжения на неинвертирующем, то на выходе компаратора устанавливается низкое напряжение, в данном случае нулевое. И наоборот, если величина напряжения на инвертирующем входе меньше, чем на не инвертирующем, то на выходе напряжение принимает значение высокого уровня, близкого к уровню питания. В нашем случае, когда напряжение начального смещения на неинвертирующем входе компаратора DA1 больше напряжения пилообразного генератора, поданного на второй вход, выходное напряжение (диаграмма 2 на рис. 101) имеет высокий уровень. Ко входу ИC 4 подключены дискретные элементы каскадов только с положительным напряжением питания. Смещение на не инвертирующем входе DA1 на величину 100 мВ является минимальным, и приращение напряжения на ИC 4 может только увеличить его. Поэтому можно сделать вывод о том, что длительность импульсов, формируемых на выходе DA1, при данном начальном смещении имеет минимальное значение и с повышением напряжения на выводе ИC 4 длительность импульсов положительной полярности будет только увеличиваться. Какое влияние это свойство оказывает на работу всей схемы управления, будет рассмотрено ниже. Периодическая последовательность импульсов с выхода компаратора DA1 поступает на цифровой логический элемент типа ИЛИ - DD1. Частота следования импульсов определяется временными характеристиками пилообразного напряжения.

На диаграмме 3 рис. 101 показано пилообразное напряжение и напряжение обратной связи U3, которое в зависимости от действия дестабилизирующих факторов может изменяться(рис. 100).

Усилитель ошибки на элементе DA3 проводит сравнение напряжения обратной связи и опорного напряжения, уровень последнего определяется соотношением резисторов R23 и R24, подключенных между выводом ИC 14 и общим проводомрис. 100. Внутренний каскад схемы ИС формирует на выводе ИC 14 стабильное напряжение с номинальным значением +5 В. Резисторы R23 и R24 образуют делитель напряжения, средняя точка которого подключена через вывод ИC 2 к инвертирующему входу операционного усилителя DA3. На неинвертирующий вход DA3 через два резистора R29 и R30 поступает напряжение от выходов вторичных каналов напряжения со значением, например, +5 В. Вход ИC 1 через резистор R25 подключен к общему проводу вторичного питания. Величины сопротивлений резисторов R25 и R29, R30, образующих делитель, подобраны таким образом, что при номинальных значениях выходных вторичных напряжений на выводе ИC 1 устанавливается напряжение чуть ниже значения +2,5 В. Этим создано некоторое начальное дифференциальное смещение на входах DA3. Усилитель DA3 работает в линейном режиме, параметры усиления определяются внутренней схемотехникой этого каскада. Питание DA3 осуществляется только от внутреннего источника с положительным значением напряжения. Следовательно, изменение выходного напряжения на DA3 может происходить только в положительной области. Для выполнения этого условия напряжение на выводе ИC 1 не должно превышать +2,5 В. Превышение этого порога приведет к тому, что на выходе DA3 установится напряжение с нулевым значением. Далее будем предполагать, что этого не происходит, и схема работает в некотором заданном для зоны регулировки диапазоне.

Итак, на входе ИC 2- напряжение постоянное, а на вход ИC 1 с нагрузки поступает напряжение обратной связи, которое имеет отклонение, определяемое возмущающими факторами. На выходе усилителя DA3 формируется сигнал рассогласования, или ошибки, точность которого определяется параметрами стабильности внутреннего источника опорного напряжения микросхемы ИC. Понятно, что все его отклонения от номинала будут передаваться на ИC 2. Выход DA3 подключен к не инвертирующему входу ШИМ компаратора - DA2, на второй его вход подается пилообразное напряжение от генератора. Формы различных сигналов на входах DA2 показаны на диаграмме 3, приведенной на рис.101. Линией, пересекающей «пилу», изображено напряжение на не инвертирующем входе DA2. Внешний вид результирующего сигнала на выходе DA2 представлен на диаграмме 4 (см. рис. 101). Видно что импульсы положительной полярности формируются здесь в том случае, когда уровень напряжения, поданного с выхода DA3, превышает уровень линейно нарастающего напряжения на инвертирующем входе DA2. На диаграмме 4 показано, как происходит изменение длительности положительных импульсов и соответственно паузы между ними в зависимости от формы напряжения на выходе DA3. Длительность положительного импульса увеличивается по мере возрастания уровня на выходе DA3, то есть продолжительность импульса прямо пропорциональна уровню напряжения на выходе усилителя рассогласования.

Последовательность импульсов подается на второй вход цифрового элемента DD1, на первый вход которого поступает импульсный сигнал с выхода DA1 - компаратора «мертвой зоны».

Элементы микросхемы ИC, работа которых описана выше, входят в аналоговую часть обработки и формирования сигналов. Необходимо отметить, что компараторы занимают здесь пограничное положение. Получая по входам аналоговые сигналы, на выходах они формируют двухуровневый сигнал. Компоненты же с буквенным обозначением DD относятся к элементам исключительно цифровой автоматики, работающими с дискретными сигналами как по входам, так и по выходам. Сигналы имеют только два уровня. В позитивной логике (этой терминологии мы будем придерживаться и далее) логической единицей принято считать значение напряжения, близкое к уровню положительного питания. Уровень логического нуля - низкий уровень, близкий к потенциалу общего провода.

Выходное состояние элемента DD1, логическое ИЛИ, принимает значение логической единицы тогда и только тогда, когда хотя бы на одном (произвольном) из его входов сигнал также имеет высокий логический уровень. Выход считается в состоянии низкого уровня, когда на все входы логического элемента типа ИЛИ подводятся напряжения также низкого уровня.

Вид импульсных выходных сигналов элемента DD1 представлен на диаграмме 5. Последовательность, полученная на выходе DD1, является базовой для формирования конечного управляющего воздействия на силовые элементы усилителя мощности. Все временные соотношения конечного сигнала уже заложены в этой исходной последовательности. Выход DD1 соединен со счетным входом С динамического триггера - DD2, а также с одним из входов каждого из логических элементов DD5 и DD6.

Состояние выходов динамического триггера изменяется с поступлением положительного фронта импульса на его счетный вход. В этот момент состояние информационного входа, вывод D, «переписывается» (повторяется) на прямой выход триггера - вывод Q. Выход (-Q) всегда имеет состояние противоположное Q (диаграммы 6 и 7).

На функциональной схеме, представленной на рис.99, показано, что динамический триггер DD2 (D-триггер) имеет соединение инверсного выхода с информационным входом - D. Такое подключение триггера устанавливает его в режим деления частоты импульсной последовательности, поступающей на счетный вход, на два. Срабатывание триггера, то есть изменение состояния его парафазных выходов, происходит только в момент поступления на вход С положительного фронта импульса. В это время каждый из его выходов меняет свое состояние на противоположное. Выводы Q и D соединены между собой, поэтому любое изменение состояния выхода Q передается на вход D. В результате каждый фронт, поступающий по входу С, переписывает на выходы измененный уровень входа D. Между приходом двух фронтов состояние выходов триггера сохраняется стабильным, что показано на диаграммах 7 и 6 (см. рис.101). Диаграмма 7 соответствует состоянию прямого выхода триггера -вывод Q, а диаграмма 6 - изменению состояния инверсного выхода - вывод (-Q). Переключение триггера происходит по положительным фронтам последовательности диаграммы 4.

Процесс цифрового деления исходной частоты на два имеет важную особенность: независимо от вида (временных соотношений импульсов и пауз) входного импульсного сигнала, в последовательности, полученной в результате деления, длительности импульсов и пауз будут равны (см.диаграммы 7 и 6 на рис. 101).

Выход Q триггера DD2 подключен к одному из входов элемента DD3, а инверсный выход (-Q) -к одному из входов логического элемента DD4. Двухвходовые элементы DD3 и DD4 выполняют функцию логического И. Элементы этого типа формируют на выходных выводах сигналы высокого логического уровня в случае, когда все их входы имеют также высокие уровни. При любой иной комбинации логических уровней на входах элемента И выход его будет оставаться низким. Все входы логического элемента оказывают одинаковое воздействие на формирование выходного сигнала, то есть они равноправны. Если на один из входов постоянно подавать высокий логический уровень, то он окажется разрешающим и не будет воздействовать на прохождение через элемент сигнала со второго входа. Или иначе, все изменения сигнала, установленного на втором входе, будут точно повторяться на выходе.

На рис.100 вывод микросхемы ИC 13 соединен с одним из входов элементов DD3 и DD4 и может быть использован для блокировки импульсных сигналов, поступающих на элементы DD3 и DD4 от выходов триггера DD2. Блокировка осуществляется подачей на этот вывод сигнала низкого логического уровня. В данной принципиальной схемерис.100. вывод ИC 13 постоянно соединен с ИC 14 - выходом источника внутреннего опорного напряжения. Этот потенциал является постоянным разрешением для прохождения последовательностей от выходов триггера на выходы DD3 и DD4. Следовательно, форма напряжения на входах и выходах элементов соответственно DD3 и DD4 будет идентична (диаграммы 9 и 8, рис.101) В данном случае эти элементы выполняют функции буферных элементов и повторителей.

Последние элементы, установленные в цепи формирования ШИМ сигнала, это двухвходовые элементы DD5 и DD6. По одному входу этих элементов подключено к DD3 и DD4 соответственно, а другая пара входов элементов DD5 и DD6 объединена между собой и подключена к выходу DD1. Элементы DD5 и DD6 используются для исполнения логической функции типа ИЛИ-НЕ. Эти элементы осуществляют логическую операцию, аналогичную DD1, но добавляют еще и отрицание, которое в цифровой технике эквивалентно инвертированию. На выходе логического элемента ИЛИ-НЕ появляется сигнал низкого уровня, когда хотя бы на одном из его входов установлено напряжение высокого уровня. Если у двухвходового элемента ИЛИ (ИЛИ-НЕ) ввести некоторое абстрактное различие между входами и один рассматривать как информационный, а второй - как разрешающий, то можно сделать вывод о том, что для прохождения данных от первого входа на выход элемента на входе разрешения должен быть установлен низкий уровень напряжения. При подаче высокого уровня на вход разрешения информация блокируется, и на выходе постоянно присутствует низкий уровень. Это справедливо для логики работы элемента типа ИЛИ-НЕ.

На входе DD5 действуют сигналы, поступающие от выходов DD1 (см. диаграмму 4 на рис. 101 и DD3 (см. диаграмму 7). В результате логического сложения этих входных воздействий с инвертированием на выходе элемента DD5 появляется сигнал, показанный на диаграмме 8. Аналогично на диаграмме 9 представлена форма импульсов, полученных на выходе элемента DD6. Импульсы положительной полярности поступают на выходы DD5 и DD6, когда оба входных сигнала у каждого из этих элементов принимают значение низкого уровня.

и DD6, когда оба входных сигнала у каждого из этих элементов принимают значение низкого уровня.

Из диаграмм 4, 8 и 9 видно, что на выходах элементов DD5. и DD6 появляются чередующиеся импульсы последовательности диаграммы 4. Рабочими импульсами на диаграмме 4 будем считать временные интервалы, границы которых очерчены спадом и фронтом, то есть начало импульса - это спад положительного напряжения, а его окончание - положительный фронт. Один импульс с выхода DD1 поступает на выход элемента DD5, а входной сигнал на DD6 в этот момент блокирован высоким уровнем, поданным от инвертирующего выхода триггера DD2. Следующий импульс из последова-тельности на выходе DD1 появляется уже на выходе DD6, а в DD5 он блокируется высоким уровнем, поступающим от прямого выхода триггера DD2. На выходе каждого из логических элементов DD5 и DD6 поочередно появляются импульсы из последовательности, сформированной на выходе DD1.

На выходах DD5 и DD6 формируются две последовательности импульсов. Частота следования импульсов в каждой из них в два раза ниже, чем частота пилообразного напряжения на конденсаторе С18. Импульсы положительной полярности двух последовательностей разнесены во времени, то есть интервалы их действия не пересекаются. Далее каждая последовательность используется для управления своим транзистором полумостового импульсного усилителя мощности. Достаточно важным является вопрос корректного формирования импульсных последовательностей для возбуждения транзисторной схемы усилителя мощности, поэтому необходимо рассмотреть некоторые граничные случаи работы схемы источника питания и реакцию на них элементов микросхемы ИC.

Временное положение импульсов жестко определено формой пилообразного напряжения. Спады импульсов в каждой из последователь-ностей синхронизированы со спадами линейно нарастающего напряжения, формируемого генератором микросхемы. Временное положение спада не изменяется. Если рассмотреть диаграмму 3, то можно отметить, что положе-ние спада импульса, формируемого ШИМ компаратором (см. диаграмму 4), зависит oт текущего соотношения значений напряжения «пилы» и напряже-ния рассогласования. Понижение уровня напряжения рассогласования на диаграмме 4 вызывает «сдвиг» начала импульса влево. Положение фронта этого импульса, то есть его окончание, жестко определяется моментом спада пилообразного напряжения, следовательно, происходит увеличение его длительности. Частота импульсов не изменяется, а их длительность регулируется выходным уровнем усилителя рассогласования DA3.

В начале описания работы ШИМ преобразователя упоминалось о так называемом компараторе «мертвой зоны» (см. диаграммы 1 и 2). Теперь, когда стал понятен общий механизм работы всей схемы широтно-импульсного модулятора, следует пояснить необходимость его наличия в схемах подобного типа.

На элементе DD1 производится логическое сложение импульсных сигналов от компараторов DA1 и DA2. Ранее было сделано предположение, что положительный импульс компаратора DA2 имеет большую ширину, чем аналогичный выходной импульс от DA1. Однако, если начнется процесс сужения импульса от DA2, то при нулевом уровне сигнала от DA1 в предельном случае на выходе DD1 установится постоянный низкий уровень. Триггер DD2 не сможет проводить коммутацию своих выходов, а на DD5 и DD6 появятся постоянные противоположные логические уровни. При этом остановится процесс коммутации транзисторов силового каскада. Для защиты от возникновения подобной ситуации предназначен компаратор «мертвой зоны». При сужении импульса от DA2 наступает такой момент, когда длительность положительного импульса от DA1 становится опреде-ляющей при сложении сигналов, поступающих на входы DD1. Положи-тельный импульс на выходе DD1 не может быть 'уже выходного импульса компаратора «мертвой зоны». Если проследить поведение цифровой части схемы в этом случае, то будет видно, что в результате преобразований на выходах DD5 и DD6 появятся последовательности положительных импуль-сов, длительности которых будут совпадать с паузами (логическими нулями) на диаграмме 2. Пауза же между этими импульсами будет равна длитель-ности положительных импульсов на диаграмме 2. Это означает, что узел на компараторе «мертвой зоны» гарантированно обеспечивает появление в выходных каскадах ШИМ преобразователя последовательностей импульсов с заданными интервалами пауз между импульсами. Такой механизм действий позволяет увеличить поступление энергии во вторичную цепь и возобновить процесс ШИМ регулирования с помощью усилителя DA3 и компаратора DA2. Пауза, образованная за счет наличия источника 100 мВ на входе DA1, позволяет исключить появление сквозных токов в силовых транзисторах усилителя мощности.

Появлением импульсных сигналов на выходах элементов DD5 и DD6 заканчивается логическая обработка сигнала рассогласования и формирование ШИМ последовательностей в преобразователе. Вид этих последовательностей импульсов останется неизменным до их подачи на силовые элементы усилителя мощности. Все каскады, установленные между выходами элементов DD5, DD6 и базовыми цепями транзисторов усилителя мощности, предназначены только для увеличения энергетических характеристик импульсов управления и согласования их уровней.

Внутренние транзисторы VT1 и VT2 микросхемы ИС используются для первичного усиления управляющих последовательностей импульсов, которые подаются на их базы (см. диаграммы 10 и 11, рис.101) от элементов DD5 и DD6. Выводы этих транзисторов не имеют внутренних подключений к каким-либо нагрузочным резистивным цепям. Они специально оставлены свободными для применения транзисторов в различных вариантах схем включения.

Непосредственное подключение выходных транзисторов микросхемы TL494 к силовому трансформатору используется редко. Обычно применяется каскад промежуточного усиления, построенный на транзисторах, например, типа 2SC945. При этом эмиттеры транзисторов VT1 и VT2 микросхемы (9,10) соединены между собой, а их коллекторы (8 и 11) имеют трансфор-маторную связь с усилителем мощности. Это традиционный подход к форми-рованию цепей согласования низковольтного, относительно маломощного узла управления и силового высоковольтного каскада. Реализация такого подхода сводится к следующему. Импульсы напряжения прямоугольной формы (см. диаграммы 12,13, рис.101) на коллекторах транзисторов VT1 и VT2 подаются на базы двух транзисторов (на рис.100 они не показаны), коллекторы и эмиттеры которых включены в первичную обмотку (схема со средней точкой) маломощного согласующего высокочастотного трансформа-тора TV2. Импульсы напряжения прямоугольной формы с вторичной обмот-ки этого трансформатора подаются на вход мощных транзисторов, включен-ных в первичную обмотку силового трансформатора TV1 (схема со средней точкой), со вторичной обмотки которого напряжение(я) поступает через выпрямитель(и) и сглаживающий (е) фильтр(ы) к потребителям электричес-кой энергии.

Таким образом, рассмотренный каскад служит для усиления по уровню и мощности импульсных сигналов ИС (диаграммы 12,13, рис.101), до уровня, достаточного для запуска полумостового (или выполненного по другой схеме) усилителя и поддержания напряжения на потребителях в пределах заданного при действии возмущающих факторов.

В импульсных ИВЭП в первичную обмотку силового трансформатора TV1 часто включают транзисторы типа 2SC945 или их функциональные аналоги. Они применяются очень широко независимо от фирмы-производителя изделия. Предельные значения основных технических параметров указанных транзисторов следующие:

· максимальная мощность рассеивания – 250 мВт;

· напряжение коллектор-база – 60 В;

· напряжение коллектор-эмиттер – 50 В;

· напряжение эмиттер-база – 5 В;

· ток коллектора – 100 мА;

· ток базы – 20 мА;

· типовое значение коэффициента усиления в схеме с общим эмиттером – 185-200;

· типовая емкость перехода коллектор-база – 3 пФ;

· типовое значение частоты единичного усиления ft – 250 МГц.

По отечественной классификации они принадлежат к семейству транзисторов высокой частоты и малой мощности.