Функции алгебры логики и их основные свойства.

Глава 1.

Москва

Конспект лекций

Схемотехника ЭВМ

Ю.В.Шаповалов

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ

ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

МИНИСТЕРСТВО

_________________________

(НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ)

_________________________

I.УСЛОВИЯ РАБОТЫ И ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ ЭВМ

1.1.ТРЕБОВАНИЯ, ПРЕДЪЯВЛЯЕМЫЕ К ЭЛЕМЕНТАМ

И УСТРОЙСТВАМ ЭВМ

Основой для составления тактико-технического задания (ТТЗ) на проектирование и разработку элементов и устройств ЭВМ могут быть:

1. Условия работы. В ТТЗ указывают диапазон рабочих температур, наличие и величину температурных толчков, максимальную влажность воздуха, частоту и амплитуду вибраций, величину динамических нагрузок. Оговаривают также устойчивость к запылению, агрессивным средам и т.д.

2. Источники питания. Источники питания современных ЭВМ занимают значительную часть общего объема оборудования. Поэтому в ТТЗ

указывают вид тока, частоту, напряжение и потребляемую мощность. Оговаривают необходимость применения стабилизаторов и их тип, а также количество используемых номиналов напряжений и допустимый их разброс.

З. Конструктивные требования. Конструктивное оформление элементов ЭВМ весьма разнообразно. Для удобства монтажа и наладки устройств элементы должны компоноваться на типовом элементе замены (ТЭЗ). Конструкция элементов и устройств должна обеспечивать их взаимозаменяемость. Кроме того, конструктивное исполнение, способ монтажа, выбранный тип разъемных соединений должны обеспечивать минимальную величину монтажных емкостей, требуемый температурный режим, заданную ремонтоспособность. При выборе конструкции необходимо учитывать также технологичность изготовления, габариты и требуемую степень герметизации.

4. Быстродействие. Быстродействие системы элементов характеризуется следующими параметрами:

а) рабочей частотой, т .е. максимальной частотой входных сигналов в наихудших, но допустимых условиях эксплуатации;

б) временем переключения td , которое определяется временем включения tdl и выключения td2 схемы:

5. Совместимость входных и выходных сигналов. Это требование означает, что электрические характеристики входных и выходных сигналов должны быть выбраны таким образом, чтобы обеспечить возможность непосредственной работы элементов один на другой без применения специальных согласующих элементов.

6. Полнота системы элементов. Выбор функционально—полной системы переключательных функций с технической точки зрения эквивалентен выбору типов элементов, из которых может быть построена любая схема ЦВМ. Поэтому при выборе функционально-полных систем переключатель-

ных функций следует исходить из технических соображений.

7. Эффективное использование элементов. При проектировании модулей ЦВМ для предварительной оценки эффективности использования оборудования необходимо знать:

а) коэффициент объединения по входу М;

б) коэффициент разветвления по выходу N;

в) добротность схемы Q;

г) произведение частоты переключения на количество компонентов в кристалле f n;

д) статические и динамические характеристики.

8. Помехозащищенность и помехоустойчивость. Эти параметры являются одними из важнейших, так как не только показывают, какую величину помехи допускает схема, но и характеризуют качество системы элементов в целом. Чем выше допустимая величина помехи, тем уже область существования передаточной характеристики, т.е. тем меньше разброс характеристик элемента.

9. Разброс параметров. Современная промышленность выпускает схемы, большинство параметров которых отличается от номинальных на ±5, ±10, ±15% в зависимости от класса точности аппаратуры.

Устройства ЦВМ необходимо рассчитывать таким образом, чтобы при их изготовлении не требовался индивидуальный отбор.

10. Удельная производительность модуля B:

где n - количество компонентов; V — объем модуля.

11. Надежность. Надежность ЦВМ определяется надежностью устройств и их элементов.

1.2.СРАВНИТЕЛЬНАЯ ОЦЕНКА ЭФФЕКТИВНОСТИ ПРИМЕНЕНИЯ

ЭЛЕМЕНТОВ ЦВМ

Для сравнительного анализа элементной базы целесообразно использовать методику оценки эффективности применения элементов ЦВМ, по которой выбирается и анализируется ряд параметров каждой схемы рассматриваемой серии, таких, например, как надежность, объем, масса, мощность рассеяния, помехозащищенность, быстродействие, нагрузочная способность, количество источников питания и т .п. Каждый из этих параметров подсчитывается по формуле

где Bi - тип схемы; Ci - процентное содержание схем в устройстве; Pi-параметр выбранной серии; Р - параметр упрощенной модели.

По вычисленным параметрам составляют матрицу обобщенных параметров Р

и матрицу нормированных параметров  относительно наихудших значений условной серии

относительно наихудших значений условной серии

где  в случае максимального наихудшего значения;

в случае максимального наихудшего значения;

в случае минимального наихудшего значения.

в случае минимального наихудшего значения.

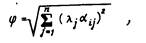

Из этих матриц определяют коэффициенты функциональных единиц φ:

где λj - весовой коэффициент, отображающий степень важности рассматриваемых параметров в проектируемой ЦВМ и их

При расчете схем обычно принимают следующие степени важности параметров: надежность – λ1 = 0,4; масса – λ2 = 0,15; объем – λ3 = 0,1; мощность рассеяния – λ4 = 0,1; помехозащищенность – λ5 = 0, I; нагрузочная способность – λ6 = 0,05; быстродействие – λ7 = 0,05; количество источников питания – λ8 = 0,05.

Поясним примером методику выбора элементной базы, наиболее часто используемых на борту летательных аппаратов. В табл.2 приведены основные сравнительные характеристики некоторых физических параметров элементов (на примере реализации одноразрядного комбинационного сумматора). По рассматриваемой методике определены коэффициенты функциональных единиц для данных систем элементов, для чего составлена нормированная матрица условных элементов(табл.3).

Из анализа табл. З можно сделать вывод, что наиболее оптимальными элементами, удовлетворяющими требованиям летательных аппаратов, являются интегральные схемы, обладающие наивысшим критерием эффективности ( φ = 0,45).

Таблица 1

Основные сравнительные характеристики элементов ЦВМ

| Параметры схемы | Типы схем | |||||

| тонко- пленоч- ные до- мены | магни- то-маг- нитные | полу- провод- никовые | интеграль- ные | оптико- электрон- ные | электро- механи- ческие | |

| Объем, см³ Масса, г Потребляе- мая мощ- ность, Вт Средняя за- держка на каскад, нс Частота от- казов на 1000ч рабо- ты | 0,05 | 1,5 0,1 | 0,75 0,05 | 0,02 0,35 0,01 0,02 | 0,1 | 1,2 3,2 0,4 0,06 |

Таблица 2

Нормированная матрица условных элементов

| Параметры схемы | Типы схем | |||||

| тонко- пленоч- ные до- мены | магни- то-маг- нитные | полу- провод- никовые | интеграль- ные | оптико- электрон- ные | электро- механи- ческие | |

| Объем χ3 =0,15 Масса χ2 =0,2 Мощность χ4 =0,15 Быстродейст-вие χ7 =0,1 Надежность χ1 =0,4 Критерий Эффектив- ности φ | 0,14 0,16 0,05 0,09 0,24 0,36 | 0,037 0,04 0,065 0,095 0,2 0,22 | 0,15 0,19 0,15 0,1 0,36 0,45 | 0,065 0,4 0,03 0,09 0,12 | 0,13 0,06 0,055 0,3 0,28 |

II.БАЗОВЫЕ ЭЛЕМЕНТЫ

2.1.БАЗОВЫЙ ЭЛЕМЕНТ ДИОДНО-ТРАНЗИСТОРНОЙ ЛОГИКИ

Диодно-транзисторная логическая схема (ДТЛ) изображена на рис. 1. Схема состоит из диодно-вентильной схемы (резистор R0 и диоды VD1) и инвертора на транзисторе VT1 и резисторе R1.

В этой схеме резистор R0 определяет потребляемую мощность и среднюю задержку, так как он задает ток, включающий транзистор и заряжающий емкости входных диодов и транзистора. Диоды смещения VD2 предназначены для понижения напряжения на

базе транзистора в закрытом состоянии в целях

базе транзистора в закрытом состоянии в целях

Рис. 1. Базовый элемент увеличения порога запирания и помехозащи-

диодно-транзисторной щенности схемы. Резистор R2 обеспечивает в

логики закрытой схеме достаточно большой ток через

смещающие диоды и повышает порог запирания схемы. Резистор R1 в статическом режиме служит для увеличения порога запирания схемы и уменьшения выходного сопротивления схемы в закрытом состоянии. Резистор R1 часто отсутствует в схеме.

Проиллюстрируем работу схемы, предположив, что логический нуль соответствует низкому потенциалу, а логическая единица - высокому потенциалу (положительная логика) и что хотя бы на один вход схемы подается низкий потенциал. В этом случае входной диод открыт, и ток через резистор R0 и этот диод вытекает из схемы. На базе транзистора VT1 создается низкий потенциал, и он находится в закрытом состоянии. При этом напряжение на коллекторе возрастает до величины E1-Ik0 R1≈E1 , соответствующей уровню логической единицы. Теперь предположим, что на все входы схемы поданы высокие потенциалы. В этом случае все входные диоды включены в обратном направлении и ток через резистор R0 и диоды VD2 поступает в базу транзистора, открывая его, и на выходе схемы

Рис. 2. Передаточная характеристика

логического элемента

устанавливается нулевой сигнал. Следовательно, схема при положительной логике выполняет операцию штрих Шеффера (И-НЕ).

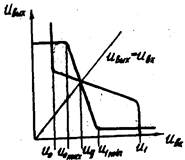

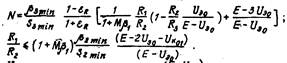

Рассмотрим более подробно алгоритм анализа ДТЛ ИС для определения следующих параметров: уровней логического сигнала U0 и U1 (рис. 2 ), ширины активной области передаточной характеристики D, размаха логического сигнала активной области передаточной характеристики D, размаха логического сигнала UЛ , запаса функциональной устойчивости S, максимального коэффициента разветвления по выходу N, средней мощности рассеяния Р и величин задержки сигнала td .

1. Уровни сигналов, соответствующие логической единице и нулю, равны

где rП.К – сопротивление “подложка-коллектор”; UП.К –напряжение “подложка-коллектор”; UО.Э –напряжение перехода “база-эмиттер”.

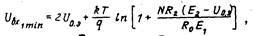

Максимально допустимая величина входного нулевого сигнала

а минимально допустимая величина единичного сигнала

где k –постоянная Больцмана; Т –температура, К; q—заряд электрона.

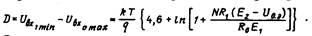

2. Ширина активной области передаточной характеристики

3. Размах логического сигнала

4. Запас функциональной устойчивости:

для уровня логического нуля

для уровня логической единицы

5. Максимальный коэффициент разветвления по выходу.

Для насыщения транзистора требуется, чтобы выполнялось условие

β IБ >-IК . Если принять, что сопротивление rП.К очень мало, и , кроме того, пренебречь током, текущим через резистор R2 , то

Отсюда для выполнения условий насыщения потребуем, чтобы

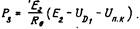

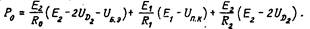

6. Средняя мощность рассеяния.

В закрытой схеме мощность рассеивается только в резисторе R0 и на входных диодах VD1 :

В открытой схеме учитываются мощности, рассеиваемые в резисторах R0 , R1 и R2 :

Выражение для средней мощности, рассеиваемой ДТЛ-схемой, имеет вид

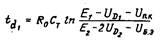

7. Задержка сигнала схемой.

Время установления при включении схемы определяется суммой времени задержки

и времени спада

где

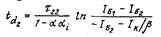

Время установления при выключении схемы также определяется суммой времени задержки

и времени нарастания tn = 0,7 R1 C1 ,

где

τ22 – постоянная времени.

Добротность схемы

Данный тип интегральной схемы имеет два существенных недостатка: во-первых, в закрытом состоянии у нее довольно большое выходное сопротивление, определяемое величиной R1; во-вторых, в процессе выключения она не может обеспечить большого выходного тока для заряда нагрузочной емкости, в результате чего при увеличении емкостной нагрузки ее быстродействие резко уменьшается.

Эти недостатки можно устранить, если использовать в схеме сложный инвертор (более подробно о нем говорится в следующем параграфе) или диоды и транзистор Шоттки.

Диод, выполненный в виде перехода металл—полупроводник , называется диодом Шоттки. Так как у разных материалов работа выхода электронов неодинакова, поверхностный слой одного из материалов будет беднее электронами, чем поверхностный слой другого. Возникает разность потенциалов между металлом и полупроводником в зоне их контакта. Разность потенциалов создает барьер (барьер Шоттки) для перехода электронов в материал с более отрицательным поверхностным зарядом. Диод Шоттки является прибором, работающим на основных носителях заряда. Вследствие этого время рассасывания носителей в диоде Шоттки равно нулю, и его быстродействие определяется только барьерной емкостью. Включение диода Шоттки параллельно переходу коллектор - база транзистора типа p—n—p позволило получить транзистор Шоттки, отличающийся малым временем рассасывания носителей и улучшенной помехоустойчивостью в наихудших условиях—при большой нагрузке и высокой температуре.

Использование указанных свойств диодов и транзисторов Шоттки дало возможность создать логические ДТЛ ИС, способные конкурировать с ТТЛ-схемами. По сравнению с обычными ДТЛ-схемами ИС на приборах Шоттки обладают лучшими помехоустойчивостью (1,5 В) и задержкой на каскад (20 нс) . Кроме того, ДТЛ ИС на приборах Шоттки имеют большой коэффициент объединения по входу и за счет высокой скорости переключения и изменяющихся сопротивлений нагрузки в цепях коллекторов транзисторов потребляют в динамическом режиме значительно меньшую мощность, чем обычные ДТЛ—схемы.

2.2. БАЗОВЫЙ ЭЛЕМЕНТ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ

Интегральные схемы транзисторно-транзисторной логики (ТТЛ ИС ) и транзисторно-транзисторной логики на приборах Шоттки (ТТЛШ) являются в настоящее время самыми распространенными логическими схемами, используемыми в устройствах вычислительных машин.

Основная ТТЛ ИС представляет собой многовходовую переключатель-

ную схему, электрическое (или логическое) состояние на выходе которой определяется логической комбинацией электрических состояний ее входа. ТТЛ ИС всех серий электрических совместимы друг с другом, и вычислительные устройства, выполненные на основе одной из них, могут быть непосредственно соединены с узлами, выполненными на основе другой, при условии соблюдения требований к нагрузочной способности схем.

Все ТТЛ работают от источников питания ЕП =5 В. Каждая схема на выходе может иметь два состояния: с низким выходным потенциалом (логический нуль), составляющим примерно 0,4 В, и с высоким выходным потенциалом (логическая единица), составляющим 2,4...4,5 В.

ТТЛ ИС обладают высоким быстродействием. Фронты сигналов их равны 4…6 нс, а задержки распространения сигналов - 8…20 нс. Диапазон входных напряжений схемы, при котором ее выходное состояние не определено, достаточно узок; выходной импеданс ТТЛ ИС мал (менее 80 Ом), что обеспечивает хорошую помехоустойчивость. Потребляемая мощность (около 20 МВт) относительно невелика. ТТЛ ИС имеют высокую нагрузочную способность. Количество входов схем ТТЛ, которое может быть подключено к выходу ТТЛ—схемы, для разных серий неодинаково, однако максимальная нагрузочная способность для серии 10 (мощная ТТЛ ИС позволяет подключить до 30 схем). Обычно ТТЛ ИС выпускаются в стандартных корпусах с количеством выводов 14, 16, 24 и предназначаются для работы в температурном диапазоне от -55 до +125 ºС.

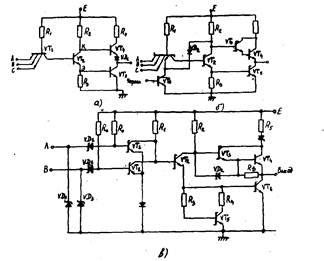

Рис. 3. Базовый элемент транзисторно-транзисторной логики:

а - схема И-НЕ; б – тристабильная схема; в – схема ИЛИ

Схема базового элемента ТТЛ ИС приведена на рис. 3,а. Она содержит три основных каскада: входной, реализующий функцию И на транзисторе VT1, фазоразделительный с возможностью реализации на нем функции ИЛИ на транзисторе VT2 и резисторах R2, R3 и выходной инвертор на транзисторах VT3 и VT4.

Количество эмиттеров у многоэмиттерного транзистора VT1 может быть различным. Обычно максимальное число эмиттеров равно тринадцати. На рис. 3,а показано только три входа, поскольку трехвходовая схемы является базовой, используемой при построении большинства ИС.

При низком потенциале хотя бы на одном из входов схемы соответствующий эмиттерный переход многоэмиттерного транзистора VT1 открыт, и на базе транзистора VT2 поддерживается низкое напряжение, недостаточное для его отпирания.

При подаче высокого потенциала на все входы схемы эмиттерные переходы VT1 закрыты, и ток через коллекторный переход VT1 поступает в базу транзистора VT2 и открывает его. Это означает, что входной транзистор выполняет логическую функцию И для положительной логики.

В трехвходовой схеме, показанной на рис. 3, а, второй транзистор VT2 представляет собой фазоразделительный каскад, обеспечивающий парафазный сигнал для управления транзисторами VT3 и VT4. Сопротивления резисторов R2 и R3 примерно одинаковы и составляют 0,25…0,33 от сопротивления R1, и поэтому для насыщения транзистора VT2 от него не требуется большого усиления по току.

В том случае, когда транзистор VT1 пропускает в базу VT2 управляющий ток (т.е. когда на все входы схемы поданы высокие потенциалы), напряжение на эмиттере VT2 (в точке Э) может возрасти только до величины UБ.Э3 , а напряжение на коллекторе VT2 (в точке К) снизится до величины UБ.Э3 + UК.Э.Н2. Когда транзистор VT1 отключает управляющий базовый ток транзистора VT2, через резисторы R2 и R3 протекает только ток утечки, поэтому напряжение в точках Э и К близки соответственно нулю и напряжению питания.

Логическая встроенная функция ИЛИ может быть выполнена при параллельном соединении двух и более подобных фазоразделительных каскадов. Если на все входы хотя бы одного из многоэмиттерных транзисторов подано высокое напряжение, то соответствующий ему фазоразделительный транзистор будет открыт. Для выключения фазоразделительного каскада необходимо на все его входы подать нулевое или близкое к нулю напряжение. Количество подключаемых схем И в такой схеме ИЛИ ограничено величиной тока утечки каждого из фазоразделительных транзисторов. При большом их количестве суммарный ток утечки может вызвать такое возрастание напряжения в точке Э, при котором выходной транзистор VT4 будет находиться на грани отпирания, что приведет к неправильному функционированию каскада.

Рассмотрим работу выходного каскада, выполняющего функцию инвертора. При низком потенциале хотя бы на одном из входов схемы соответствующий эмиттерный переход транзистора VT1 открыт, и на базе транзистора VT2 поддерживается низкое напряжение, недостаточное для его отпирания. Транзисторы VT2 и VT3 закрыты, транзистор VT4 и диод VD1 открыты и обеспечивают на выходе высокое напряжение. При высоком потенциале на всех входах схемы эмиттерные переходы VT1 закрыты, и ток через коллекторный переход поступает в базу транзистора VT2. Транзисторы VT2 и VT3 открыты, и на выходе схемы устанавливается низкое напряжение. Транзистор VT4 и диод VD1 при этом закрыты, так как разность потенциалов между коллекторами VT2 и VT3 недостаточна для отпирания цепи VT4 – VD1.

Резистор R4 служит для ограничения тока выходного каскада во время выключения схемы, когда транзистор VT3 еще находится в режиме насыщения, а транзистор VT4 уже открылся. Диод VD1 включается в выходной каскад для того, чтобы обеспечить запирание транзистора VT4 при низком напряжении на выходе. В противном случае эммиттерный ток транзистора VT4 вызвал бы повышение низкого напряжения на выходе.

Tак как в базовом элементе ТТЛ ИС низкое напряжение появляется на выходе схемы при подаче на все входы высоких потенциалов, то он выполняет операцию И-НЕ для положительной логики, т . е.

Рассмотрим алгоритм расчета базового элемента:

I. Задаемся типовыми значениями параметров диодов, транзисторов и резисторов.

2. Задаемся близкими к оптимальным значениям R1 / R2 = 2.. .4 и

R2 / R3 = 1…2.

3. По заданному значению S0 с помощью выражения

определяем U0max , т.е. получаем ограничения  .

.

4. По заданному значению S1 с помощью выражения

определяем U1min и , используя зависимость  находим напряжение Е. При известном Е уточняем величину R2 / R3.

находим напряжение Е. При известном Е уточняем величину R2 / R3.

5. Из выражений

по заданному значению Р и выбранным отношениям R1 / R2 и R2 / R3 определяем номиналы резисторов R1 , R2, R3 (с учетом  ).

).

6. Из соотношений

находим максимальные и минимальные значения токов открытых транзисторов.

7. C помощью  и выбранного значения S3=1,2…1,3 определяем сопротивление rк3.

и выбранного значения S3=1,2…1,3 определяем сопротивление rк3.

8. Из условия Uk2 < Uэн+UDз+U0 находим ограничения на величину Uк.н.2.

9. При заданных N, Т и Е и выбранных значениях и находим ограничения на величины β2min и β3min:

10. Из выражения  получаем значения β1max и Iвх 1у.

получаем значения β1max и Iвх 1у.

11. Полагаем, что величина предельно допустимого тока транзистора VT3 в импульсном режиме Iк3min не должна превышать величины максимального тока Iк3 в статическом режиме более чем в три раза. При выбранном значении R2 считается, что rD ≈ rк3 ≈ rк4 . С помощью выражений  определяем номинальное значение R4.

определяем номинальное значение R4.

12. В соответствии с результатом статического расчета выбираем структуру и геометрию элементов схемы—транзисторов и резисторов. Для выбранных структур определяем параметры элементов τ0 , τр , Сэ, Ск, β, оцениваем величины паразитных емкостей в различных узлах схемы СП1, СП2, СП3, СП4, СП вых. Если параметры элементов оказываются существенно отличными от принятых в пунктах 1…11, необходимо произвести повторный расчет с уточненными их значениями.

13. В соответствии с выражениями td1 = t'd1 + tc и td2 =t'd2 +tн получаем величины задержки сигнала в схеме. Если найденные значения не удовлетворяют заданию, следует произвести соответствующую коррекцию параметров элементов и повторить расчет.

14. Определяем величину динамической мощности Рg:

Если полученное значение Pg превышает заданное, то уменьшают ток Iэ4max, путем увеличения сопротивления R4.

Одним из недостатков рассматриваемой схемы является то обстоятельство, что их нельзя объединять по выходу, поскольку они имеют низкое выходное сопротивление в обоих состояниях.

Чтобы осуществить объединение по выходу; можно использовать схемы ТТЛШ с тремя состояниями (рис. 3, б). Особенность их заключается в том, что все транзисторы, кроме VT4, являются транзисторами Шоттки и, кроме того, имеется управляющий вход, который удерживает VT1 в состоянии насыщения в прямом направлении, благодаря чему закрыт VT2, а следовательно, и VT5. В то же время управляющий вход шунтирует коллекторную цепь VT2, в результате чего транзистор VT4 также закрыт. В этом случае выход находится в третьем состоянии — в состоянии, высокого выходного сопротивления.

ТТЛШ с тремя состояниями позволяют производить некоторые весьма полезные операции, связанные с коммутацией. Заметим, что в этой схеме для обеспечения большого тока нагрузки плечо выход- кого каскада выполнено по схеме Дарлингтона. В этом случае диод в выходном каскаде не требуется, так как пара составных транзисторов создает падение напряжения на двух переходах “база – эмиттер” . Поскольку в транзисторах Шоттки отсутствует накопление носителей, они могут иметь большой коэффициент усиления по сравнению с обычными схемами. Однако переход Шоттки имеет собственную емкость, поэтому соответствующая постоянная времени RС должна быть минимизирована за счет тщательной разработки конструкции.

На рис. 3, в показана ТТЛШ ИС, выполняющая логическую операцию ИЛИ и состоящая из трех каскадов: входного, реализующего операцию ИЛИ на транзисторах VT1, фазоразделительного на транзисторе VT2 и выходного каскада на транзисторах VT3…VT6.

Рассмотрим работу схемы. Предположим, что в первоначальный момент на все входы схемы подаются низкие потенциалы. В этом случае входные диоды открыты и ток протекает через R0 и VD1 на вход схемы. На базах транзисторов VT1 устанавливается низкий потенциал, а на их выходах - высокий, который открывает фазоразделительный транзистор VT2; на коллекторе VT2 — низкий потенциал, недостаточный для открывания выходного транзистора VT4; на эмиттере VT2 - высокий потенциал, который открывает транзистор VT6 и еще больше подзапирает выходной транзистор VT4, и на выходе схемы устанавливается низкое напряжение.

В том случае, если хотя бы на один вход схемы подается высокий потенциал, то и на соответствующий вход транзистора VT1 также подается высокий потенциал (входной диод смещен в обратном направлении). Транзистор VT1 открыт, и на его коллекторе устанавливается низкий потенциал, транзистор VT2 закрыт, и на его выходе устанавливается высокий потенциал, который открывает соответственно транзисторы VT3 и VT4 и переводит схему в единичное состояние.

Рассматриваемая схема имеет дополнительные особенности, которые могут быть использованы в любых схемах ТТЛ. Входы зашунтированы диодами VD3 для защиты от высокочастотной генерации, а транзистор VT5 обеспечивает быстрое выключение VT6. Коэффициенты усиления транзисторов возрастают с повышением температуры, что приводят к увеличению времени закрывания VT6. Вместе с тем с ростом температуры увеличивается сопротивление резистора а его влияние уменьшается. В схему введен транзистор VT5, носящий название активного шунта. С повышением напряжения ток через этот транзистор возрастает и компенсирует температурные изменения.

Основные характеристики двухвходового базового элемента ТТЛ и ТТЛШ, выполняющего логические функции штрих Шеффера, ИЛИ и исключающая ИЛИ, приведены в табл. 3.

Таблица 3.

Основные характеристики схем ТТЛ и ТТЛШ

| Тип ИС | Логическая схема схема | Параметры | |||||||||||||||||||

| Напряжение пита- ния E, B | Uвх1 min , B a | Uвх0 max , B | Uвых1 , B | Uвых0 , B | Iвх1 , мкА | Iвх0 , мА | Iвых1 , мкА | Iвых0 , мА | td1 , нс | td2 , нс | td , нс | P , мВт | N | ||||||||

| ТТЛ | И-НЕ | 0,4 | 0,2 | -1,6 | |||||||||||||||||

| ИЛИ | 0,4 | 3,4 | 0,2 | -1,6 | -800 | ||||||||||||||||

| Исклю- чаю- щая ИЛИ | 0,4 | 3,4 | 0,2 | -1,6 | -800 | ||||||||||||||||

| ТТЛШ | И-НЕ | 0,4 | 0,5 | -2 | 4,5 | 4,7 | |||||||||||||||

| ИЛИ | 0,4 | 3,4 | 0,25 | -0,36 | -400 | 4,5 | 4,5 | 4,5 | |||||||||||||

| Исклю- чаю- щая ИЛИ | 0,4 | 3,4 | 0,5 | -2 | -1 | 6,5 | 17,5 | ||||||||||||||

2.3.БАЗОВЫЙ ЭЛЕМЕНТ С ИНЖЕКЦИОННЫМ ПИТАНИЕМ

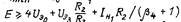

На рис. 4 показан элемент, относящийся к схемам с двойной инжекцией (ИИЛ), которые также называются многоколлекторными логическими схемами (МКЛ).

Рис. 4. Базовый элемент с инжекционным питанием:

а - конструкция; б – принципиальная схема;

в—логическая схема

Транзистор с инжекционным питанием представляет собой четырехслойную структуру p1 – n1 – p2 - n2 -типа (рис. 4,а), в которой можно выделить два транзистора n – p – n – и p – n – p –типа. Транзистор p – n – p - типа образован инжекторной p1 - областью, играющей роль эмиттера, частью эмиттерной n1 - области, служащей базой, и базовой p2- областью, выполняющей функции коллектора. Транзистор n – p – n -типа с вертикальным расположением электродов образован частью эмиттерной n1 -области, примыкающей к ней частью базовой p2 -области и коллекторной n2 – областью. Заметим, что в логических элементах данного типа не требуется ни изолирующих областей, ни резисторов, что позволяет достичь высокой плотности интеграции.

Рассмотрим более подробно работу базового элемента. Предположим, что эмиттер схемы заземлен; между этим электродом и инжектором включен внешний источник ЭДС, обеспечивающий прямое смещение инжекторного перехода, а цепи базы и коллектора разомкнуты.

Тогда из инжектора в эмиттер инжектируются дырки. В эмиттерной области у инжекторного перехода возникает избыточная концентрация дырок. Для нейтрализации заряда инжектированных дырок в змиттерную область через внешний вывод поступают электроны. Концентрация избыточных электронов приблизительно равна концентрации избыточных дырок. Вследствие появления градиента концентрации происходит диффузия электронов и дырок к эмиттерному переходу. Дойдя до эмиттерного перехода, избыточные электроны компенсируют часть объемного заряда перехода, обусловленного ионизированными донорами. Избыточные дырки захватываются полем перехода и, попадая в область перехода со стороны базы, компенсируют часть объемного заряда ионизированных. акцепторов. В результате эмиттерный переход сужается и потенциальный барьер его понижается, т. е. переход смещается в прямом направлении. Часть избыточных электронов и дырок из области эмиттера проходит в область базы. Переход электронов эквивалентен их инжекции из эмиттера в базу, а переход дырок обеспечивает электрическую нейтральность базы.

Избыточные электроны и дырки, диффундируя к коллекторному переходу, компенсируют часть объемного заряда перехода, и его потенциальный барьер понижается. В результате коллекторный переход смещается в прямом направлении, а транзистор оказывается в режиме насыщения. Напряжение между коллектором и эмиттером определяется как

где α1i - инверсный коэффициент усиления транзистора n – p – n.

Выходное сопротивление n – p – n -транзистора, находящегося в режиме насыщения, невелико, и его можно рассматривать как ключ в замкнутом состоянии. Если p2 -базу с помощью ключа соединить с эмиттером, то инжекция электронов в базу прекратится. Разность потенциалов, на эмиттерном переходе окажется равной нулю, и ток в цепи базы будет

где α2N — коэффициент усиления транзистора p – n – p ; IИ — ток инжектора.

В коллекторной цепи ток отсутствует, и транзистор переходит в активный режим на границе с режимом отсечки. Его выходное сопротивление при этом резко увеличивается, что соответствует разомкнутому ключу. Таким образом, даже при закороченной цепи эмиттер – база через базу n – p – n –транзистора протекает ток, величина которого определяется IИ. Это позволяет представить транзистор схемой замещения, содержащей генератор тока в цепи базы (рис. 4, б). Величина тока IГ = α2N IИ схемы замещения определяется количеством дырок, инжектируемых через прямосмещенный инжекторный переход и собираемых базой n – p – n –транзистора.

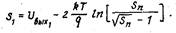

Для анализа возможности использования ИИЛ-элемекта в логических схемах рассчитывает некоторые его электрические характеристики.

Функция, обратная передаточной характеристике, т.е. зависимость  определяется из соотношения

определяется из соотношения

где Sn — степень насыщения:  , BN - коэффициент усиления , N—нагрузочная способность схемы.

, BN - коэффициент усиления , N—нагрузочная способность схемы.

Величины выходных единичного и нулевого сигналов равны

Запас помехоустойчивости составляет:

для уровня логического нуля

Для уровня логической единицы

Помехоустойчивость и быстродействие схем ИЛИ возрастают с увеличением инжекторного тока. Однако одновременно повышается рассеиваемая мощность. Величина PD для логических элементов составляет I пДж. Для уменьшения значения PD используют разные конструктивные решения. Так, схема с трехсторонней конструкцией

инжектора И³Л позволяет снизить паразитную емкость боковых стенок n – p – n —транзистора, схема с боковым p – n – p -транзистором, получившая название логической схемы с перехватом тока (ПТЛ), собирает на коллекторе заряд, исходящий от эмиттера, и управляет током подложки.

В базовой схеме ИИЛ (рис. 4,в), собранной на основе двух транзисторов, сигнал логической единицы (отсутствие выходного тока) на выходе будет в том случае, если на оба входа А и В подан логический нуль. В этом случае ток инжектора VT1 и VT2 отводится от баз этих транзисторов на вход схемы, транзисторы закрыты, и элемент реализует логическую функцию штрих Шеффера.

Основное назначение ИИЛ—схемы –использование в матрицах БИС и микропроцессорах.

2.4.БАЗОВАЯ СХЯА ЛОГИКИ НА ПЕРЕКЛЮЧАТЕЛЯХ ТОКА

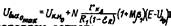

Базовый логический элемент (рис. 5), выполняющий функцию И/И-НЕ, состоит из трех электрических каскадов: токового переключателя на транзисторах VT2 и VT3, выходных змиттерных повторителей VT1 и VT4 источника опорного напряжения, собранного на транзисторе VT5, резисторах R4, R5, R6 и диодах VD1, VD2.

Рис. 5. Базовый элемент транзисторной логики

на переключателях тока

Токовый переключатель предназначен для выполнения логических функций (первая ступень логики), в том числе для образования парафазного сигнала (прямого и инверсного), формирования и усиления входного сигнала по напряжению и обеспечения заданной помехоустойчивости. Токовый переключатель представляет собой дифференциальный усилитель, работающий в ключевом режиме. В одной ветви диффе- ренциального усилителя расположены входные транзисторы VT2, в другой — транзистор VT3. Обе ветви связаны через резистор R2, так что VT3 открыт только в том случае, если на всех входах схемы имеются сигналы низкого уровня. При этом падение напряжения на R2 обеспечивает закрывание транзисторов VT2; транзистор VT4 открыт, и ток течет через R3, VT3, R2. Обычно R2 в несколько раз больше R1 и R3 , что позволяет получать ток постоянной величины в ветвях дифференциального усилителя при переключении его из одной ветви в другую в соответствии с сигналами управления.

Для наличия хотя бы на одном из входов схемы сигнала, с высоким уровнем напряжения один из транзисторов VT1 открывается , и возросшее падение напряжения на R2 , закрывает транзистор VT3 ток переключается в левую ветвь. Тем более, ток переключается при нескольких сигналах высокого уровня на входах схемы.

Сигналы с коллекторных нагрузок левой и правой ветвей дифференциального усилителя через эмиттерные повторители поступают на прямой и инверсный выходы схемы. Выходные эмиттерные повторители предназначены для выполнения логических функций (вторая ступень логики), усилении сигнала по мощности, работы на согласованные линии связи, а также для смещения выходных сигналов по напряжению в целях обеспечения совместной работы с другими злементами.

Источник опорного напряжения предназначен для получении напряжения, относительно которого происходит переключение тока в токовом переключателе, равного среднему уровню напряжения между выходными уровнями сигналов логического нуля и единицы.

При переключении тока в токовом переключателе входными управляющими сигналами выполняется функция И/И-НЕ для отрицательной логики и функция ИЛИ/ИЛИ-НЕ—для положительной.

Особенностью базовой схемы является подключение всех входов к шине питания через резистор Rвх , что исключает необходимость ориентации неиспользованных входов на определенный потенциал. Кроме того , в целях снижения потребляемой мощности и организации согласованных линий связи нагрузочные резисторы выходных эмиттерных повторителей вынесены за пределы схемы и размещены в отдельных корпусах.

Для расширения логических возможностей базовой схемы. и получения второй ступени логики используется объединение двух или нескольких выходов элементов на одном нагрузочном сопротивлении эмиттерного повторителя (эмиттерный ДОТ). При объединении прямых выходов получается двухступенчатая функция И , а при объединении инверсных выходов – функция И-ИЛИ-НЕ.

Если объединить несколько схем на одном коллекторном сопротивлении, то получим выполнение функции ИЛИ (коллекторный ДОТ). Для предотвращения режима насыщения транзистора прямого плеча схемы в случае протекания увеличенного тока через коллекторное сопротивление предусматривается включение дополнительной цепи подсечки на транзисторе и резисторе.

Для получения сложных логических функций при сохранении высокого быстродейст- вия применяются двухуровневый и трехуровневый принципы переключения схемы, когда эмиттерным током верхнего уровня переключения является коллекторный ток нижнего уровня, предварительно переключаемый входными сигналами по определенной функции. Для управления вторым и третьим уровнями переключения на входе базового элемента предусматривается включение эмиттерных повторителей, обеспечивающих смещение входных уровней сигналов. Для стабилизации переключаемого тока генератор в этих схемах строится на транзисторе и резисторе.

Высокое быстродействие схем на переключателях тока (ПТТЛ) , составляющее 0,5. . .1,0 нс, обусловлено как низким выходным импедансом, благодаря чему они могут работать на емкостную нагрузку, так и тем, что они используются в ненасыщеннном режиме. Перепад напряжений логических уровней этих схем составляет 800 мВ, что затрудняет их сопряжение с элементами других серий. Следует отметить, что ток, потребляемый этими схемами от источника питания, почти постоянен, если не принимать во внимание нагрузку. Он не зависит от состояния ПТТЛ, поскольку происходит коммутация тока внутри схемы, а следовательно, не образуются паразитные броски тока, имеющие место в ТТЛ-схемах. Выходные транзисторы обладают высоким коэффициентом усиления, и так как они включены по схеме с общим коллектором, то при низком выходном сопротивлении могут обеспечивать выходной ток порядка 50 мА. В результате такие схемы имеют высокий коэффициент разветвления по выходу (при RН = 100 Ом N = 30).

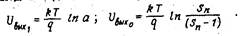

При анализе ПТТЛ ИС основным выражением является зависимость

(I)

(I)

где

Алгоритм анализа схемы включает в себя:

I. Выбор величины источника опорного напряжения (ИОН). Допустим, что сопротивление эмиттера rэ ≈ 0, г, токи I3 = I4 и напряжения Uб.э 5 = Uд.см

Из выражения (I) получим

(2)

(3)

(3)

где β –статический коэффициент усиления транзистора ;

Из (2) и (З) найдем величину ИОН

(4)

(4)

где коэффициент

Так как γ / β << I то третьей составляющей вследствие ее малости можно пренебречь, и окончательно величина ИОН определяется как

(5)

(5)

2. Определение величины напряжения переключения. Исследуем зависимость выходного напряжения дифференциального усилителя VT2 и VT3 от разности напряжений между его входами U12 . За счет R1 и R2 плечи дифференциального усилителя симметричны по выходному напряжению, и расчет производится относительно выхода VT4 :

(6)

(6)

где

Из (6) найдем

(7)

(7)

где

С учетом допущения, что  , используя (7), получаем

, используя (7), получаем

(8)

(8)

(9)

(9)

Если принять, что динамический коэффициент усиления дифференциального усилителя равен единице, то величина напряжения переключения, соответствующая границе помехоустойчивости, определится как

(10)

(10)

В связи с тем, что при переключении схемы из одного состояния в другое весь ток из транзисторов VT2 переходит в транзистор VT3 и наоборот, e  >> I и

>> I и

(II)

(II)

. (12)

. (12)

Из (II) и (12) находят граничное значение напряжения переключения U12.

3. Определение уровней напряжения на выходе схемы. Из(I), (8) и (9) получаем

(13)

(13)

(14)

(14)

где

L – коэффициент объединения по выходу; N — коэффициент разветвления по выходу.

4. Определение запаса помехоустойчивости:

для уровня логической единицы

(15)

(15)

для уровня логического нуля

(16)

(16)

Основные параметры базовых элементов ПТТЛ, выполняющих логические операции стрелка Пирса, дизъюнкции, исключающая ИЛИ приведены в табл. 8.

Таблица 4

Основные параметры ПТТЛ-схем

| Логические схемы схема | Параметры | |||||||||||||||||||

| Напряжение пита- ния E, B | Uвх1 min , B a | Uвх0 max , B | Uвых1 , B | Uвых0 , B | Iвх1 , мкА | Iвх0 , мА | Iвых0 , мА | IП , мА | td1 , нс | td2 , нс | P , мВт | N | ||||||||

| И/ И- НЕ | -5,2 | -2,1 | -0,45 | -1,625 | -0,72 | 0,5 | 2,9 | |||||||||||||

| Исклю- чаю- щая ИЛИ | -5,2 | -2,1 | -0,45 | -1,65 | -0,81 | 0,5 | 7,5 | |||||||||||||

| И-НЕ с боль- шим быстро-дейст- вием | -5,2 | -2,1 | -0,45 | -1,85 | -0,9 | 0,5 | 1,5 | 2,5 | ||||||||||||

2.5.БАЗОВЫЕ УНИПОЛЯРНЫЕ МДП—СХЕМЫ

Основными компонентами униполярных схем являются транзисторы. Униполярными транзисторами называются полупроводниковые приборы, работа которых основана на модуляции сопротивления слоя полупроводникового материала поперечным электрическим полем. В настоящее время известны две разновидности схем: полевые транзисторы с управляющими p – n -переходами и транзисторы со структурой металл — окисел (диэлектрик) - полупроводник (МДП). Типовые структуры этих приборов приведены на рис. 6,а.

Рис. 6. Базовые униполярные схемы:

а – типовые структуры; б – статическая

схема; в – динамическая схема

Транзистор с управляющим p – n -переходом является трехполюсным полупроводниковым прибором. Он представляет собой p – n -переход, смещенный в обратном направлении, вдоль слоя которого между электродами стока и истока протекает ток основных носителей. В полевых транзисторах истоком называется электрод, от которого начинается движение основных носителей в канале, стоком — электрод, к которому направляются основные носителя, затвором - управляющий электрод. В транзисторах с управляющими p – n -переходами изменение проводимости канала осуществляется за счет изменения толщины слоя пространственного заряда p – n-перехода под действием напряжения, приложенного к управляющему электроду и смещающего p – n -переход в обратном направлении.

В МДП—транзисторах изменение проводимости граничного слоя между окислом и полупроводником происходит за счет наведения заряда подвижных носителей под действием напряжения, приложенного к затвору. МДП-транзиторы классифицируются на транзисторы со встроенными каналами и транзисторы с индуцированными каналами. В транзисторах со встроенными каналами канал между стоком и истоком создается технологическим путем. В транзисторах с индуцированными каналами последние наводятся под действием управляющего напряжения. Транзисторы со встроенными каналами могут работать в режимах обогащения и обеднения канала основными носителями, а транзисторы с индуцированными каналами — только в режиме обогащения граничного слоя окисел - полупроводник основными носителями. По типу проводимости каналов транзисторы делятся на транзисторы с каналами n - и р -типов. Схемы, состоящие одновременно из транзисторов

n – и р -типов, называются комплиментарными МДП-схемами (КМДП).

Рассмотрим более подробно работу МДП-транзистора. При заземленных стоке и истоке затвор управляет зарядом в канале. При подаче на затвор отрицательного напряжения условия в объеме кремния изменяются. По мере того как на затворе накапливается отрицательный заряд, свободные электроны, присутствующие в кремние n -типа, вытесняются из прилегающей к затвору области, и в ней образуется обедненный слой. При достижении определенной степени обеднения продолжающееся увеличение смещения затвора вызывает притяжение к поверхности кремния подвижных положительных заряженных дырок. Когда в области канала накопится достаточное количество дырок, тип проводимости поверхности кремния изменится с электронной на дырочную, т.е. произойдет инверсия типа проводимости. При этом две диффузионные области р —типа окажутся соединенными друг с другом посредством инверсного слоя с проводимостью р -типа, служащего каналом. Отсюда и название - МДП-транзистор с каналом р -типа. Подавая на затвор сигнал, можно модулировать количество носителей в области канала, так что затвор, по существу, регулирует ток, протекающий в канале. При малой величине напряжения на стоке инверсный слой распространяется на всю область канала, соединяя области истока и стока. При таких условиях ток стока зависит от напряжений на стоке и затворе. При постоянном напряжения на затворе повышение напряжения на стоке изменяет условия в области накала. Ток стока вызывает омическое падение напряжения вдоль канала. Причем полярность этого падения напряжения такова, что оно стремится противодействовать полю, создаваемому в слое окисла смещением затвора. Когда падение напряжения достигает величины, при которой поле уменьшается настолько, что инверсный слой больше не возникает, ток стока стремятся к постоянной величине, не зависящей от напряжения на стоке.

Следует сказать также о пороговом напряжении. Пороговое напряжение — это напряжение на слое окисла под затвором, необходимое и достаточное для начала формирования в канале инверсного слоя. При дальнейшем повышении напряжения на стоке МДП—транзистор переходит в состояние глубокого насыщения. Слишком большое напряжение стока может вызвать сквозное обеднение, что приведет к возникновению неконтролируемого тока.

Основные соотношения для МДП-транзисторов:

I) крутая область:

2) область насыщения:

Предельная частота переключения ограничивается паразитной емкостью:

где gm - крутизна характеристики; с - емкость слоя диэлектрика под затвором.

Особенностью МДП-структур является использование в них только униполярных транзисторов. Это связано с тем, что функции диффузионных транзисторов могут выполнять сами МДП—транзисторы; схемы на МДП—транзисторах — это схемы с непосредственными связями, и поэтому нет необходимости в конденсаторах связи; вследствие использования многотактных импульсов синхронизации отпадает необходимость в блокировочных конденсаторах.

Основные уравнения для расчета МДП-схем приведены в табл. 9.

Таблица 9

Основные уравнения для расчета МДП-схем

| Параметры | Тип МДП-транзистора | |

| p - канал | n - канал | |

| Тип проводимости подложки Полярность напряжения E Пороговое напряжение Uпор Объемный заряд в обедненной области QВ Эффективный заряд в окисле и на поверхности раздела Q0x Потенциал уровня Ферми ФF Изгиб зон в начале инверсии ФF Работа выхода электрона из металла в кремний ФMS Эффективная поверхностная подвижность µ Концентрация легирующей примеси в подложке Z Ширина канала w Длина канала l Пороговое напряжение Заряд в обедненной области Ток крутой области Напряжение пологой области | n - - + + + - - µp = + ZD | p + + - + - + - µp = - ZА |

| ||

Для построении логических МДП ИС используются две базовые схемы: в одной из них входные МДП-транзисторы соединены последовательно, в другой — параллельно. Логические операции, выполняемые такими схемами, зависят от типа логики входных сигналов. Так как входное напряжение схемы с последовательно включенными входными транзисторами должно быть близко к нулю, когда два входных транзистора открыты, суммарное сопротивление входных транзисторов должно быть равно сопротивлению входного транзистора простейшего инвертора. Для уменьшении сопротивления размеры каждого из последовательно включенных транзисторов до