Сигма-дельта АЦП

АЦП считывания

АЦП последовательного приближения

В АЦП последовательного приближения биты формируются единственным высокоскоростным и высокоточным компаратором последовательно один за другим от старшего к младшему, который сравнивает аналоговый вход с выходом ЦАП, чей выход обновляется прежде, чем определяется очередной бит. Эта последовательная процедура ограничивает быстродействие несколькими миллионами преобразований в секунду, и даже менее при большом (14-16 бит) разрешении. В конвейерном АЦП все секции работают параллельно, определяя небольшое число бит каждая (от последовательных выборок). Компаратор в АЦП последовательного приближения один, но он должен быть быстрым (его быстродействие определяется произведение числа разрядов АЦП на частоту преобразования) и настолько же точный, как сам АЦП. В конвейерных АЦП, напротив, ни от одного из компараторов не требуется такого быстродействия и точности.

Однако конвейерный АЦП требует для реализации много больше площади кремния, чем АЦП последовательного приближения. Задержка АЦП последовательного приближения составляет один цикл (1/Fsample), у конвейерных она 3 и более циклов. Оба типа АЦП требуют подгонки и калибровки при числе разрядов более 12.

Несмотря на внутренний параллелизм, конвейерный АЦП требует точного усиления в ЦАП и промежуточных усилителях и, следовательно, значительного времени для установления их сигналов. АЦП считывания имеет большой банк компараторов, но только их напряжения переключения должны быть согласованы. Как результат никакой конвейерный АЦП не может достичь производительности АЦП считывания.

Хотя существуют сверхбыстрые 8 разрядные АЦП считывания (например, МАХ104/МАХ106/МАХ108) с частотой преобразования 1,5 Gsps, очень трудно найти 10-разрядный АЦП считывания, а 12-разрядный АЦП является коммерчески недоступным продуктом. Это просто потому, что в них число компараторов возрастает в два раза на каждый дополнительный бит разрешения, в то же время в два раза возрастают требования к их точности. В конвейерных АЦП порядок сложности тоже возрастает, но линейно, а не экспоненциально.

При одинаковой частоте преобразования конвейерные АЦП имеют меньшее энергопотребление, чем АЦП считывания. Они также менее чувствительны к неоднозначности состояния компараторов – в АЦП считывания это явление может привести к непредсказуемым выбросам результата преобразования.

Традиционные сигма-дельта АЦП, используемые в цифровом аудио, имеют ограниченную полосу около 22 кГц. Но недавно появились широкополосные АЦП с полосой от 1 до 2 МГц с разрешением от 12 до 16 бит.

3.3 АЦП последовательного приближения[Д13]

АЦП последовательного приближения являются популярной архитектурой для аналого-цифрового преобразования с разрешением от среднего до высокого и производительностью до 5 Msps. Обычный диапазон разрешения составляет у них от 8 до 16 бит при малом энергопотреблении и габаритах. Такая комбинация характеристик делает АЦП последовательного приближения идеальным для широкого круга применений, таких как портативные приборы с батарейным питанием, устройства промышленной автоматики и системы сбора и обработки информации.

Как следует из названия, АЦП последовательного приближения используют алгоритм двоичного перебора, поэтому у них частота преобразования составляет лишь часть от тактовой частоты (несколько мегагерц), на которой работает внутренняя структура.

Архитектура АЦП последовательного приближения

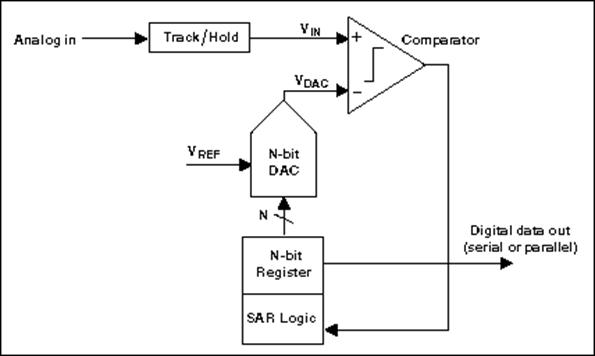

Базовая блок-схема АЦП последовательного приближения приведена на рис.3.3.1. Входной сигнал Vin выбирается и сохраняется на время преобразования устройством выборки/хранения. Реализуя алгоритм двоичного выбора N-разрядный регистр сначала устанавливается на середину шкалы (т.е. в состояние 1000…00, устанавливая в 1 старший разряд). Этот код устанавливает на выходе ЦАП напряжение, равное половине опорного напряжения Vref. Компаратор производит сравнение напряжений чтобы определить, больше входное напряжение Vin выходного напряжения Vref/2 ЦАП или меньше. Если оно больше, на выходе компаратора «1» и старший разряд регистра остается в состоянии «1», если меньше - на выходе компаратора «0» и старший разряд регистра устанавливается в состоянии «0». Затем управляющая логика сдвигается на один бит вниз и устанавливает в единицу соответствующий бит регистра, т.е. на середину выбранной в первом такте половины шкалы, и производится следующее сравнение напряжений и так до младшего разряда регистра. По окончании процесса в регистре оказывается N-разрядный код, соответствующий Vin.

Рис.3.3.2 иллюстрирует процесс преобразования в 4-разрядном АЦП. Видно как жирная линия, отображающая выходное напряжение VDAC ЦАП приближается к линии входного напряжения Vin. В этом примере результат сравнения напряжений в первом такте Vin <VDAC и бит 3 регистра устанавливается в «0». ЦАП затем устанавливается во втором такте в состояние 0100 и производится следующее сравнение, результат которого Vin >VDAC и бит 2 остается в состоянии «1». ЦАП затем устанавливается в третьем такте в состояние 0110 и производится третье сравнение. Поскольку результат сравнения Vin <VDAC бит 3 устанавливается в состояние «0» и на ЦАП в четвертом такте подается 0101 для последнего сравнения, в результате которого бит 0 остается в состоянии «1» поскольку Vin >VDAC.

Рис.3.3.1

Заметим, что для формирования кода АЦП потребовалось четыре такта. В общем случае АЦП последовательного приближения требуется N тактов для полного цикла преобразования и следующий цикл не может начаться ранее, чем закончится предыдущий. Это объясняет, почему этот тип АЦП эффективен по энергопотреблению и габаритам, но трудно найти приборы с быстродействием несколько Msps при разрешении 14-16 разрядов.

Рис.3.3.2

Одни из самых малогабаритных АЦП, представленных на рынке, базируются на архитектуре последовательного приближения. Например, семейство МАХ1115 – МАХ1118 8-разрядных АЦП и их аналоги с большим разрешением МАХ1086 и МАХ1286 (10 и 12 разрядов, соответственно) упакованы в корпус SOT23 с размерами 3х3 мм.

Другой особенностью АЦП последовательного приближения является зависимость потребления от тактовой частоты, что отличает их от АЦП считывания и конвейерных АЦП с постоянной потребляемой мощностью. Это свойство особенно полезно в маломощной аппаратуре или там, где частота выборки не постоянна.

Анализ компонентов АЦП последовательного приближения

Наиболее критичными компонентами АЦП последовательного приближения являются компаратор и ЦАП. Как будет показано ниже, устройство выборки хранения может быть совмещено с ЦАП.

Быстродействие АЦП последовательного приближения ограничивается следующими факторами:

- временем установления ЦАП, который должен устанавливаться с точностью всего АЦП, например 1/2LSB;

- компаратором, который должен различать малые разности между Vin и VDAC за определенное время;

- задержками в логике.