А)Структура процессорного ядра МК и основные характеристики, определяющие производительность процессорного ядра.

Вопросы

К 3 ступени Государственного экзамена

по дисциплине «Микропроцессоры и микропроцессорные системы»

для специальности 230101 «Вычислительные машины, комплексы, системы и сети»

Процессорное ядро микроконтроллера.

А) Структура процессорного ядра МК и Основные характеристики, определяющие

Производительность процессорного ядра.

Б) Организация процессов выборки и исполнения команд: Фон- Неймановская и

Гарвардская архитектуры.

В) Изображение схемы структур МПС с Фон- Неймановской и Гарвардской

архитектурой.

- Основные этапы разработки микропроцессорной системы на основе микроконтроллера.

А) Основные этапы разработки микроконтроллера.

Б) основные характеристики при выборе типа МК.

- Основные факторы, влияющие на быстродействие процессора. Регистры процессора.

А) Регистры процессора.

Б) Сегменты команд, данных и стека в памяти.

В) Факторы, влияющие на быстродействие процессора.

Преподаватель _____________ Набиева Н.А.

ОТВЕТЫ

По дисциплине «Микропроцессоры и микропроцессорные системы»

Специальность 230101 «Вычислительные машины, комплексы, системы и сети»

1. Процессорное ядро микроконтроллера. Основные характеристики, определяющие производительность процессорного ядра. Процессоры с CISC и RISC архитектурой.

Процессорное ядро микроконтроллера

А)Структура процессорного ядра МК и основные характеристики, определяющие производительность процессорного ядра.

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

-набор регистров для хранения промежуточных данных;

-система команд процессора;

-способы адресации операндов в пространстве памяти;

-организация процессов выборки и исполнения команды.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализует один из двух принципов построения процессоров:

-процессоры с CISC-архитектурой, реализующие так называемую полную систему команд (Complicated Instruction Set Computer);

-процессоры с RISC-архитектурой, реализующие сокращенную систему команд (Reduced Instruction Set Computer).

С точки зрения организации процессов выборки и исполнения команды в современных 8-разрядных МК применяется одна из двух уже упоминавшихся архитектур МПС: фон-неймановская (принстонская) или гарвардская.

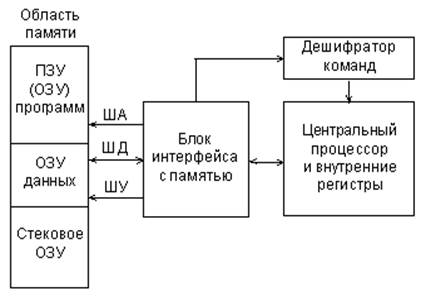

Основной особенностью фон-неймановской архитектуры является использование общей памяти для хранения программ и данных, как показано на рис. 4.2.

Рис. 4.2. Структура МПС с фон-неймановской архитектурой.

Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МПС с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтому фон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных, как показано на рис. 4.3.

Рис. 4.3. Структура МПС с гарвардской архитектурой.

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению.