Транзисторно – транзисторная логика.

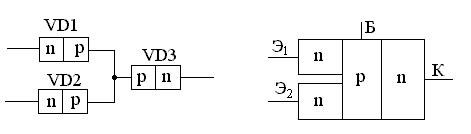

На рисунке 1.10а представлена структура диодов VD1-VD3 схемы ДТЛ. В интегральном исполнении области р можно объединить, и тогда получится структура изображенная на рисунке 1.10б. Эта структура представляет собой транзистор с двумя эмиттерами (двухэмиттерный транзистор).

а) б)

Рисунок 1.10

Если в предыдущей схеме ДТЛ диоды VD 1, VD 2 и VD 3 заменить на двухэмиттерный транзистор, то получится транзисторно – транзисторная логика (ТТЛ), принципиальная схема которой приведена на рисунке 1.11.

Рисунок 1.11

В качестве VT1 можно использовать транзистор с большим числом эмиттеров, схема в этом случае будет иметь соответствующее число входов.

Принцип работы, таблица истинности и характеристики ТТЛ такие же, как у ДТЛ.

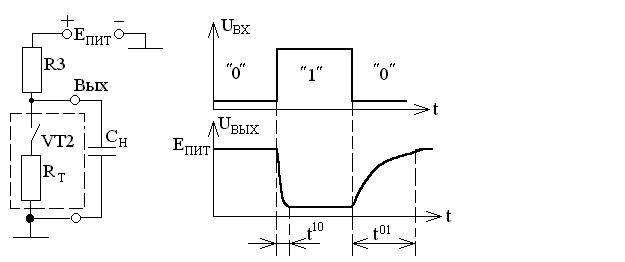

Недостаток предыдущих схем заключается в следующем. Заменим транзистор VT2 ключом с сопротивлением RТ (рисунок 1.12а).

В исходном состоянии (на входе схемы логический ²0²), транзистор закрыт (ключ разомкнут), на выходе напряжение равно напряжению питания ЕПИТ (рисунок 1.12б). При подаче на вход логической ²1²ключ замыкается. В этом случае ёмкость нагрузки СН разряжается через малое сопротивление ключа RT и время включения будет составлять t10. При подаче на вход логического²0² ключ вновь размыкается и, в этом случае, ёмкость СН будет заряжаться через сопротивление R3, которое намного больше, чем RT и время выключения будет t01> t10, из-за этого быстродействие схемы будет низким.

а) б)

Рисунок 1.12

Кроме того между точкой А и общим проводом находятся два pn-перехода, следовательно на эмиттерном переходе при подаче на вход логического ²0² напряжение будет составлять 0,4 В и для того, чтобы открыть транзистор надо приложить меньшее напряжение, т.е. помехо-устойчивость схемы снижается.

Задача состоит в том, чтобы снизить t01 (t01» t10) и повысить помехоустойчивость.