Кодеры и декодеры с линейной шкалой квантования

Кодеры цифровых систем передачи с ИКМ-ВРК предназначены для преобразования АИМ сигналов после их квантования в цифровую форму. Операции квантования и кодирования в современных ЦСП с ИКМ-ВРК обычно совмещаются. Если квантование осуществляется с постоянным шагом (равномерное), то такие кодеры называются кодерами с линейной шкалой квантования, если же шаг квантования изменяется (нелинейное квантование), то такие кодеры называются кодерами с нелинейной шкалой квантования. В ЦСП с ИКМ применяются кодеры с нелинейной шкалой квантования, но при их построении на первой ступени кодирования используются кодеры с линейной шкалой квантования. Поэтому вначале рассмотрим принципы построения и функционирования кодеров с линейной шкалой квантования.

Различные типы кодеров, использующихся в ЦСП с ИКМ-ВРК, по принципу их действия разделяют на три группы:

- с преобразованием кодируемой величины во временной интервал

(кодеры последовательного счета);

- поразрядного сравнения (взвешивающие кодеры);

- с кодовым полем (матричные кодеры).

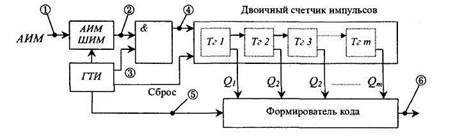

Кодеры последовательного счета.Структурная схема одного из вариантов кодера последовательного счета приведена на рис. 2.6, а временные диаграммы, поясняющие принцип его работы показаны на рис. 2.7

Рис. 2.6. Функциональная схема кодера последовательного счета

Квантованный АИМ сигнал (рис. 2.7 - 1) поступает на преобразователь АИМ сигнала в широтно-импульсно-модулированный сигнал АИМ-ШИМ (рис. 2.6, точка 7), где преобразуется в импульсы ШИМ сигнала одинаковой амплитуды, но различной длительности (рис. 2.6, точка 2).

Длительность импульсов ШИМ сигнала г^,им пропорциональна амплитуде импульсов входного АИМ сигнала (рис. 2.7 - 2). Эти импульсы поступают на схему И, на другой вход которой от генератора тактовых импульсов (ГТИ) поступают короткие эталонные импульсы с постоянным периодом следования (рис. 2.6, точка 3 и рис. 2.7 - 3). Пока схема И открыта благодаря воздействию ШИМ импульса, на ее выходе формируется

пакет эталонных импульсов (рис. 2.6, точка 4 и рис. 2.7—4).

Длительность пакета пропорциональна длительности ШИМ импульса, а следовательно число импульсов в пакете пропорционально амплитуде квантованного входного АИМ сигнала. Количество импульсов, входящих в пакет, подсчитывается двоичным счетчиком (цепочка последовательно соединенных триггеров Тг 1.. .Тг т, где т - разрядность кодовой комбинации).

Длительность пакета пропорциональна длительности ШИМ импульса, а следовательно число импульсов в пакете пропорционально амплитуде квантованного входного АИМ сигнала. Количество импульсов, входящих в пакет, подсчитывается двоичным счетчиком (цепочка последовательно соединенных триггеров Тг 1.. .Тг т, где т - разрядность кодовой комбинации).

Результат счета устанавливается на кодовых выходах счетчика Qi...Qm и выражает двоичный эквивалент кодируемого сигнала в параллельном коде, который с помощью формирователя кода преобразуется в последовательный код (рис. 2.6, точка 6 и рис. 2.7 - 6). Импульсы сброса от ГТИ (рис. 2.6, точка 5 и рис. 2.7 - 5) поступают на вход двоичного счетчика и возвращают его в исходное состояние после формирования каждой кодовой комбинации. В кодере такого типа погрешности кодирования вызываются нестабильностью частоты ГТИ, нелинейностью преобразования АИМ-ШИМ, ошибками работы двоичного счетчика и конечной разрешающей способностью схемы И.

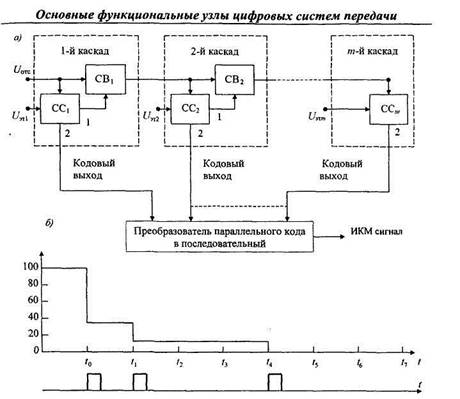

Кодеры поразрядного сравнения,или взвешивающие кодеры, нашли самое широкое применение в ЦСП с ИКМ-ВРК. Структурная схема такого кодера и временные диаграммы, поясняющие общие принципы его работы, приведены на рис. 2.8,а и 2.8,6 соответственно.

Кодирование в такой схеме аналогично процессу взвешивания тяжести при помощи набора гирь на чашках весов. После помещения взвешиваемого предмета на чашку весов устанавливают гирю наибольшего веса, по результату первой операции взвешивания принимают решение: если взвешиваемый предмет тяжелее гири, то ее оставляют на весах и дополнительно устанавливают на чашку гирю меньшего веса; а если взвешиваемый предмет легче гири, то перед установкой второй гири первую снимают и т.д. до полного уравновешивания предмета набором гирь.

В схеме рис. 2.8,а происходит последовательное сравнение кодируемого сигнала с рядом эталонных сигналов, равных 2т~' -8о, где т - число разрядов в кодовой комбинации, i - номер разряда, 80 - шаг равномерного квантования. Кодируемый отсчет АИМ сигнала Umc поступает на схему сравнения СС\ 1-го каскада, где он сравнивается с эталоном наибольшего

веса £/ЭТ1, равным 2т~' -до-

Если напряжение входного сигнала Umc больше напряжения [/эть то на выходе 1 схемы CQ появится напряжение, равное 2т~' §о, которое вычитается из сигнала в схеме вычитания СВ{; при этом на вход второго каскада кодера подается напряжение Up\, а на выходе 2 схемы СС\ формируется первый символ кодовой комбинации. Если напряжение кодируемого отсчета Uorc меньше £/ет1, то он проходит через схему СВХ без изменения, так как в этом

Рис. 2.8. Обобщенная структурная схема кодера поразрядного кодирования (а) и временная диаграмма его работы (б)

случае на выходе 1 напряжение отсутствует; на выходе 2 этой же схемы формируется пробел (нуль) кодовой комбинации. Следующие каскады кодера работают аналогичным образом. Число каскадов кодера равно числу разрядов в кодовой комбинации, которое, в свою очередь, связано с числом уровней квантования М соотношением М = 2т. Если, например, кодируемый сигнал квантуется 128-ю уровнями, то кодер состоит из семи каскадов.

Кодовая комбинация формируется в виде параллельного кода, который для целей передачи преобразуется в последовательный код ИКМ сигнала.

Поясним процесс кодирования числовым примером. Пусть амплитуда отсчета АИМ сигнала U0TC = 100 80. При 7-разрядном кодировании эталонные напряжения имеют следующие значения: £/„1 = 64 80, и„г = 32 50, f/этз = 16 50, Un4 = 8 50, U3t5 = 4 50, {/эт6 = 2 80, U3r7 = 80. Процесс формирования кодовой комбинации представлен на рис. 2.8,6.

Отсчет с амплитудой U0TC, подлежащий кодированию, устанавливается на входе кодера в момент времени O...to, затем происходит его сравнение с эталоном С/ЭТ1- При этом на кодовом выходе первого каскада будет сформирована 1, а на вход второго каскада кодера поступает разностный сигнал t/pi = Umc -1/ет1 = 100 50 - 64 50 = 36 80.

Отсчет с амплитудой U0TC, подлежащий кодированию, устанавливается на входе кодера в момент времени O...to, затем происходит его сравнение с эталоном С/ЭТ1- При этом на кодовом выходе первого каскада будет сформирована 1, а на вход второго каскада кодера поступает разностный сигнал t/pi = Umc -1/ет1 = 100 50 - 64 50 = 36 80.

Аналогичным образом на кодовом выходе второго каскада будет сформирована вторая 1, а на вход третьего каскада поступит разностный сигнал, равный £/Р2 = f/pi -С/ЭТ2 = 36 5о -32 5о = 4 6V Очевидно, на кодовых выходах третьего и четвертого каскадов кодера будут сформированы 0, так как разностный сигнал, равный 4 5о, меньше эталонов третьего и четвертого каскадов. Разностный сигнал поступит на схему сравнения пятого каскада, для которого £/ЭТ5 = 4 SV В этом случае возможны два исхода:

1) на кодовым выходе пятого каскада будет сформирована 1, и процесс

поразрядного сравнения и вычитания на этом прекратится, так как разно

стный сигнал на входах шестого и седьмого каскадов будет равен нулю;

2) на кодовом выходе пятого каскада будет сформирован 0, на вход

шестого каскада поступит разностный сигнал, равный 450, и на его выходе

будет сформирована 1. Аналогично, на вход седьмого каскада поступит

разностный сигнал, равный 2 5<ь и на его кодовом выходе будет также

сформирована 1.

В идеальном кодирующем устройстве возможен лишь первый исход, так как такое устройство четко реагирует на соотношение t/p,- > £/эт,- кодового импульса 1. При этом на выходе кодера будет сформирована кодовая комбинация вида 1100100, соответствующая (64 + 32 + 0 + 0 + 4 + 0 + 0) 5о= 100 5о.

В реальном кодирующем устройстве возможна некоторая неопределенность решения, так как схема, реагирующая на соотношение £/р,- > U^i, может быть выполнена лишь с конечной точностью. При втором исходе формируется кодовая группа, соответствующая (64 + 32 + 0 + 0 + 0 + 2+1)5о = 998о.

Из рассмотренного примера следует, что возможны дополнительные искажения сигналов, обусловленные конечной точностью осуществления процессов сравнения и вычитания, конечной стабильностью и точностью установки эталонных напряжений (токов) и т.п. По аналогии с шумами квантования эти искажения называются шумами кодирования и относятся к классу инструментальных погрешностей.

Рассмотренная схема кодера взвешивающего типа или поразрядного кодирования формирует натуральный двоичный код однополярного сигнала.

Структурная схема кодера, приведенная на рис. 2.8,а, поясняет только принцип поразрядного кодирования. Она может быть видоизменена с целью

Рис. 2.9. Обобщенная структурная схема кодера с декодером в цепи обратной

связи

достижения тех или иных технических целей. Так, например, включением на выходе каждой схемы вычитания усилителя с коэффициентом усиления, равным двум, или удлинителя (аттенюатора) с коэффициентом передачи, равным Уг, кодер может быть построен с использованием одного эталонного напряжения. Введение в схему кодера обратной связи при сохранении числа эталонов, равного т, позволяет уменьшить количество схем сравнения до 1 (рис. 2.9).

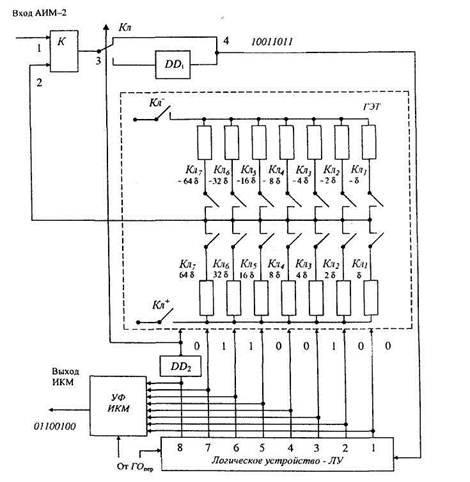

Принцип построения линейного кодера с обратной связью для кодирования однополярных положительных сигналов при использовании 7-разрядного кода (т = 7) показан на рис. 2.10.

Кодер состоит из компаратора (К), генератора эталонных токов (ГЭТ), логического устройства (ЛУ), устройства формирования ИКМ сигнала (УФ ИКМ). Последовательный характер процесса кодирования требует сохранения величины отсчета с высокой точностью в течение всего периода кодирования. Поэтому на вход кодера поступает сигнал АИМ-2. Процессы кодирования и формирования выходного сигнала происходят в УФ ИКМ под воздействием управляющих сигналов, поступающих от генераторного оборудования передающей станции (ГОпер). Формирование эталонных токов осуществляется подключением общего источника опорного напряжения Е к цепочке, сопротивления отдельных ветвей которой связаны друг с другом двоичными соотношениями вида 2м R, где номер разряда i принимает значения 1, 2, 3, ..., т. Подключение источника опорного напряжения к той или иной ветви происходит по командам, вырабатываемым ЛУ и воздействующим на ключи Кл\...Кл1. В исходном состоянии, предшествующем началу первого такта кодирования, все ключи разомкнуты, их сопротивления в идеальном случае бесконечно велики и токи /эт в ветвях ГЭТ равны нулю. Поступление соответствующей команды с ЛУ вызывает замыкание ключа Кль источник опорного напряжения подключается к одному из прецизионных резисторов и формирует эталонный ток /„,-, определяемый двоичным соотношением вида 2т~' 8, который поступает на вход 2 компаратора К

Компаратор К осуществляет сравнение сигналов на входах 1 и 2. Если напряжение на входе 1 больше или равно напряжению на входе 2, то сигнал на выходе 3 компаратора равен логическому 0, если UBXi меньше UBx2, то на выходе 3 компаратора будет сигнал логической 1. Работой ГЭТ управляет ЛУ, алгоритм работы которого выбирают таким образом, чтобы последовательным включением и выключением эталонов установилось приближенное равенство сигналов на входах 1 и 2 компаратора. В соответствии с принципом взвешивания происходит процесс постепенного уравновешивания кодируемого сигнала суммой эталонов. Работу кодера рассмотрим на примере кодирования АИМ-2 отсчета, равного /отс = 100 б. Перед началом кодирования все ключи Кл].. .Кл7 разомкнуты (рис. 2.10).

|

| Рис. 2.10. Линейный кодер взвешивающего типа для однополярного сигнала Рис. 2.10. Линейный кодер взвешивающего типа для однополярного сигнала |

Первый такт. С поступлением отсчета /отс = 100 5 на вход 1 компаратора К на 7-м выходе ЛУ, управляемого импульсами тактовой частоты Л9пер, и соответствующем входе УФ ИКМ появляется 1. Ключ #7 замыкается, и на вход 2 компаратора К поступает эталонный сигнал /3t7 = 64 8. Так как /отс = 100 8 > /ЭТ7 = 64 8, то на выходе компаратора К появляется 0. В результате этого ключ К7 остается в замкнутом состоянии, и на выходе УФ ИКМ появляется 1.

Второй такт. На 6-м выходе ЛУ, управляемого импульсами тактовой частоты ЛОпер, и соответствующем входе УФ ИКМ появляется 1. Ключ Кб замыкается, и на вход 2 компаратора К подается эталонный сигнал /^ = 32 8. Таким образом, на входе 2 компаратора формируется сигнал вида /эт7 + +/,т6 = 64 8 + 32 8 = 96 8. Так как /отс=100 8 > /эт7 + /этб = 64 8 + 32 8 = 96 8, то на выходе компаратора К появляется 0. В результате чего ключ Кв остается в замкнутом состоянии и на выходе УФ ИКМ появляется 1.

Третий такт. На 5-м выходе ЛУ, управляемого импульсами тактовой частоты ГОиер, и соответствующем входе УФ ИКМ появляется 1. Ключ К5 замыкается, и на вход 2 компаратора К подается эталонный сигнал /эт5 = 16 8. Таким образом, на входе 2 компаратора формируется сигнал вида /ЭТ7 + /этб + +/Эт5 = 64 5 + 32 5 + 16 8 = 112 8. Так как /отс=100 8 < /эт7 + /эт6 + /эт5 = =64 8 + 32 8 + 16 8 =112 8., то на выходе компаратора К появляется 1. В результате чего ключ ^размыкается, эталонный сигнал /эт5 = 16 8 от входа 2 компаратора отключается, на 5-м выходе ЛУ и на входе УФ ИКМ устанавливается 0, а следовательно, и на выходе кодера появляется 0. На входе 2 компаратора действует сигнал, равный /эт7 + /^ = 648 + 328 = 96 8.

Четвертый такт. На 4-м выходе ЛУ, управляемого импульсами тактовой частоты ГОжр, и соответствующем входе УФ ИКМ появляется 1. Ключ К4 замыкается, и на вход 2 компаратора К подается эталонный сигнал /эт4 = 8 8. Таким образом, на входе 2 компаратора формируется сигнал вида /эт7 + /^ + 7эт4= 648 + 328 + 88 = 1048. Так как /отс=1006</эт7 +1^,+ /ет4= = 648 + 328 + 88 =1048., то на выходе компаратора /<f появляется 1. В результате чего ключ К4 размыкается, эталонный сигнал /эт4 = 88 от входа 2 компаратора отключается, на 4-м выходе ЛУ и на входе УФ ИКМ устанавливается 0, а следовательно, и на выходе кодера появляется 0. На входе 2 компаратора действует сигнал, равный /эт7 +1^= 648 + 328 = 968.

Пятый такт. На 3-м выходе ЛУ, управляемого импульсами тактовой частоты Л9пер, и соответствующем входе УФ ИКМ появляется 1. Ключ К3 замыкается, и на вход 2 компаратора К подается эталонный сигнал /эт3 = 48. Таким образом, на входе 2 компаратора формируется сигнал /ЭТ7 + 4^ + 4гз = 648+ + 328 + 48 = 1008. Так как /„„=1008 = /эт7 + /^ + 4й = 648 + 328 + 48, то на выходе компаратора К появляется 0. В результате ключ К5 остается замкнутым

и на выходе УФ ИКМ формируется сигнал логической 1. Очевидно, что реализация шестого и седьмого тактов приводит к появлению на выходе кодера 0. Таким образом, по окончании седьмого такта кодирования на выходе кодера формируется кодовая комбинация вида 1100100. После завершения кодирования сигналы, поступающие от ЛОПер> переводят узлы кодера в исходное состояние, подготавливая его к кодированию следующего отсчета.

и на выходе УФ ИКМ формируется сигнал логической 1. Очевидно, что реализация шестого и седьмого тактов приводит к появлению на выходе кодера 0. Таким образом, по окончании седьмого такта кодирования на выходе кодера формируется кодовая комбинация вида 1100100. После завершения кодирования сигналы, поступающие от ЛОПер> переводят узлы кодера в исходное состояние, подготавливая его к кодированию следующего отсчета.

Большинство первичных сигналов являются двухполярными и, следовательно, для их кодирования необходимо применение соответствующего кодера. Для реализации кодера (рис. 2.11) требуется ГЭТ, формирующий эталонные сигналы для кодирования положительных и отрицательных отсчетов.

При необходимости кодирования 128 положительных и 128 отрицательных уровней потребуется 8-разрядная кодовая комбинация, причем высший разряд (8-й) будет кодировать полярность отсчета. При том же алгоритме работы компаратора, что и при кодировании однополярных сигналов, возникает следующая ситуация. Кодируя отсчет /„„ = 1008 и сравнивая с высшим эталоном /эт7 = 648, получим Imc - /эт7 = 1008 -648 >0. Данный эталон остается включенным. Сравнивая теперь /отс = -1008 с высшим эталоном /эт7 = -648, получим /отс - /эт7 = -1008 - (-648) < 0. Эталон при этом выключается. Для устранения указанного недостатка при кодировании отрицательных отсчетов на выходе компаратора К включается инвертор DDt значение сигналов на выходе компаратора будут инвертироваться и логическое устройство ЛУ будет принимать решение об оставлении или отключении соответствующего эталона.

Алгоритм работы линейного кодера двухполярных сигналов рассмотрим на примере кодирования отсчета отрицательной полярности /отс = -1008.

Первый такт. Кодируемый отсчет поступает на вход 1 компаратора. Импульс от генераторного оборудования ГОпер устанавливает на 8-м выходе 1. Ключ Кл+ замыкается и подключает положительные эталоны. Ключи положительных и отрицательных эталонов Клу.. .Кл\ разомкнуты. На входе 2 компаратора ток /эт = 0.

Поскольку сигнал имеет отрицательную полярность, т. е. /„„ < 0, то на выходе компаратора 3 появляется 1, которая через замкнутый ключ Кл, (выход 4) поступает на ЛУ и переводит 8-й выход в 0. При этом ключ Кл+ разомкнётся, а на выходе инвертора DD2 появится 1, ключ ЮГ, замкнется и к выходу 2 компаратора подключатся отрицательные эталоны, а ключ Кл подключит к выходу 3 компаратора инвертор DD[. Следовательно, на 8-м выходе ЛУ остается 0, который и появляется на выходе УФ ИКМсигнала.

Второй такт. Сигнал с выхода ГОпер переводит 7-й выход ЛУ в состояние 1. Ключ Кл7 отрицательных эталонов подключает к входу 2 компаратора эталон /эт7 = - 64 8. Так как разность 1тс - /эт7 = -100 8 - (-64 8) < 0, то на выходе компаратора формируется 1, а на выходе 4 инвертора DDX появляется 0 и эталонный ток /эт7 = - 64 8 остается включенным

— восьмой такты будут аналогичными ранее рассмотренным выше этапам кодирования. Последовательность решений компаратора в процессе кодирования отсчета представлена на выходе 4 DD\ (рис. 2.11) комбинацией символов 10011011.

| Рис. 2.11. Линейный кодер взвешивающего типа для двухполярного сигнала |

Здесь левый символ 1 этой комбинации прошел с выхода компаратора до включения инвертора DD\. По окончании восьмого такта кодирования на выходах ЛУ будет сформирована комбинация 01100100, представляю

| Рис. 2.11. Линейный кодер взвешивающего типа для двухполярного сигнала |

щая в 8-и разрядном симметричном двоичном коде значение амплитуды отсчета -100 8. Напомним, что символ высшего разряда кодовой комбинации определяет полярность отсчета.

щая в 8-и разрядном симметричном двоичном коде значение амплитуды отсчета -100 8. Напомним, что символ высшего разряда кодовой комбинации определяет полярность отсчета.

Матричные кодеры.Принцип работы кодирующих устройств с кодовым полем - матричных кодеров, основан на использовании физической модели кодовой таблицы. Кодовая таблица физически определяет точное взаимное соответствие между номером разрешенного уровня и расположением импульсов и пробелов в кодовой комбинации. Если в кодере взвешивающего типа кодируемый отсчет сравнивается последовательно во времени с набором эталонных сигналов, а вкодере счетного типа происходит сопоставление кодируемого отсчета с эталонным временным интервалом, то вматричном кодере сигнал сопоставляется непосредственно с физической моделью кодовой таблицы - кодовым полем. Кодовое поле может быть выполнено либо в виде набора решающих устройств, либо в виде кодовой матрицы в специализированной электронно-лучевой кодирующей трубке (ЭЛКТ). При поступлении на вход такого кодера АИМ сигнала данной амплитуды приводятся в состояние возбуждения определенные элементы кодового поля (матрицы) и на выходе кодера формируется кодовая группа, которая соответствует определенному квантованному значению отсчета.

Матричные кодеры с решающими устройствами на электронных приборах содержат большое число коммутационных элементов, обладают невысокой точностью кодирования, и потому их можно использовать при кодировании с небольшим (до пяти) числом разрядов. Матричные кодеры на основе ЭЛКТ просты по своей идее, обладают высоким быстродействием и высокой точностью кодирования, но требуют высокой точности фокусировки и юстировки, высокого напряжения, обладают сравнительно большими габаритами, недостаточной надежностью и поэтому не нашли применения в ЦСП.

Декодеры с поразрядным суммированием токов.Процесс декодирования, обратный процессу кодирования, заключается в том, что в специальном устройстве - декодере - путем преобразования кодовых комбинаций вырабатываются импульсы, амплитуда которых пропорциональна квантованным отсчетам передаваемого сигнала. Так же, как и кодирование, декодирование может быть осуществлено различными способами. По аналогии с классификацией кодеров различают счетные, взвешивающие и матричные декодеры. Самое широкое применение в ЦСП на основе ИКМ нашли декодеры взвешивающего типа с поразрядным суммированием токов. Структурная схема линейного декодера такого типа для декодирования двухполярных сигналов приведена на рис. 2.12.

Вход ИКМ

Рис. 2.12. Линейный декодер взвешивающего типа для двухполярного сигнала

Функционирование схемы рассмотрим на следующем примере. Пусть на вход декодера поступает кодовая комбинация вида 01100100, соответствующая двухполярному отсчету. Преобразователь кода ПК входящую кодовую комбинацию впоследовательном коде преобразует в параллельный код.

На выходе логического устройства ЛУ формируются сигналы управления, коммутирующие ключи эталонов соответствующих разрядов. В симметричном коде высший разряд определяет полярность отсчета. В рассматриваемой кодовой комбинации высшему разряду соответствует 0. Следовательно, на выходе инвертора DD появляется 1, которая замыкает Кл, коммутирующий отрицательные источники эталонов. Далее замыкаются ключи Клу, Кль и Кл-i, в результате чего формируется суммарный ток отрицательной полярности -100 8. Преобразователь кода ПК и логическое устройство ЛУ управляются тактовыми импульсами, поступающими от генераторного оборудования приема ГОпр

2.3. Кодеры и декодеры с нелинейной шкалой квантования

2.3. Кодеры и декодеры с нелинейной шкалой квантования

Общие принципы нелинейного квантования и соответствующего ему кодирования рассмотрены ранее (см. гл. 1, § 1.4). Рассмотрим реализацию нелинейных кодеров для наиболее распространенного закона компанди-рования А-87,6/13.

Необходимая разрядность кодовой комбинации при линейном квантовании т для речевого (двухполярного) сигнала, поступающего на вход канала тональной частоты (КТЧ) от различных источников, определяется требованиями к защищенности от шумов Ат и равна (см. гл. 1, § 1.3)

| (2.1) |

^+42,2

где Акв — допустимая защищенность от шумов квантования.

где Акв — допустимая защищенность от шумов квантования.

Помехозащищенность сигнала на выходе КТЧ по нормам МЭС-Т должна быть не менее 25 дБ. Если считать, что в КТЧ цифровых систем передачи единственным видом шумов являются шумы квантования, то у4кв = 25 дБ. Подставив значение Аа в (2.1) и округляя результат до большего целого, получим т = 12. Для кодирования двухполярных отсчетов с использованием симметричного кода кодовая комбинация будет иметь вид РХХХХХХХХХХХ, где Р — символ равный 1 или 0, определяющий полярность отсчета, а символы X, принимающие значения 1 или 0, отображают его абсолютное квантованное значение при шаге квантования, равном о0. Таким образом, для кодирования абсолютного значения квантованного отсчета требуется 11-разрядная кодовая комбинация вида

I /ото I = 21050 + 2950 + ... + 225 + 2'5 + 2°50. (2.2)

Входным сигналом для нелинейного кодера данного типа является квантованный отсчет, полученный в результате равномерного квантования с шагом квантования 80, соответствующего требованиям защищенности от шумов квантования. При линейном кодировании этому соответствует 2048 положительных и 2048 отрицательных уровней (2.2).

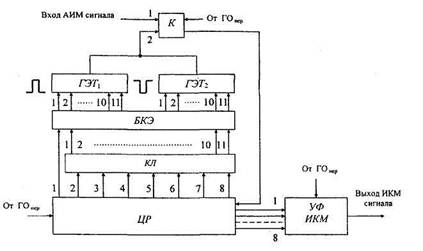

При нелинейном кодировании по закону А-87,6/13 (с коэффициентом сжатия А = 87,6 и числом сегментов для положительной и отрицательной полярности, равным восьми) для такой же защищенности от шумов квантования потребуется 128 положительных и 128 отрицательных уровней, а кодовая комбинация должна быть 8-разрядной (см. гл. 1, § 1.4, рис. 1.27, 1.28 и табл. 1.8, 1.9 и пояснения к ним). Структурная схема нелинейного кодера взвешивающего типа с цифровой компрессией эталонов приведена на рис. 2.13.

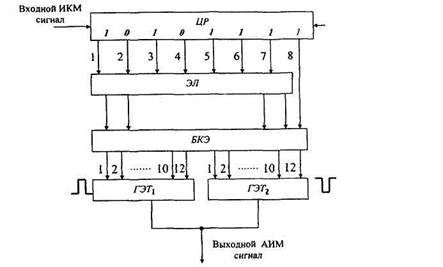

Рис. 2. 13. Структурная схема нелинейного кодера

Назначение и принцип работы компаратора К, генераторов эталонных токов ГЭТ\ и ГЭТг, устройства формирования цифрового сигнала УФ ИКМ такие же, как и в схеме линейного кодера для двухполярного сигнала. Однако в отличие от линейного кодера ГЭТу и ГЭТг содержат 11 ключей, а веса подключаемых ими эталонных токов равны 5о, 2бо, 45о,... ..., 51250 и 102450. После каждого такта кодирования решение компаратора К записывается в цифровой регистр ЦР.

В зависимости от решения компаратора ЦР выбирает полярность ГЭТ и управляет работой цифровой логики, которая преобразует 7-разрядный код в 11-разрядный и формирует в блоке выбора и коммутации эталонных токов БКЭ цепи ГЭТ, определяя величины эталонов, подключаемых на вход второго компаратора, (см. гл. 1, § 1.4. Кодирование по Л-закону ком-пандирования). Устройство формирования ИКМ сигнала УФ ИКМ считывает состояние выходов ЦР и преобразует параллельный код в последовательный.

Как было показано ранее (см. гл. 1. § 1.4. Кодирование по А -закону компандирования), кодирование осуществляется за восемь тактов и включает три основных этапа, на которых определяется и кодируется:

- полярность входного сигнала;

- номер сегмента, в котором находится кодируемый отсчет;

номер уровня квантования сегмента, в зоне которого заключена ам

плитуда кодируемого отсчета

Первый этап кодирования осуществляется за первый такт, второй этап -за второй-четвертый такты и третий этап - за пятый-восьмой такты кодирования.

Первый этап кодирования осуществляется за первый такт, второй этап -за второй-четвертый такты и третий этап - за пятый-восьмой такты кодирования.

Рассмотрим численный пример кодирования. На вход 1 компаратора К нелинейного кодера поступает положительный отсчет с амплитудой /Отс=136580.

Первый такт. С выхода генератора передачи ГОиер на первый выход ЦР поступает 1, а все остальные выходы ЦР находятся в нулевом состоянии. Это вызывает подключение к входу 2 компаратора ГЭТ, положительной полярности. Так как /отс > 0, то на выходе компаратора 3 появится О и состояние 1 на первом выходе ЦР сохранится. Эта 1 с выхода ЦР поступает на вход 1 УФ ИКМ. Следовательно, символ полярности Р=1. На этом завершается первый этап кодирования.

Второй такт. С выхода генератора передачи ГО„ер на второй выход ЦР поступает 1, на выходе 1 ЦР находится 1, выходы 3...8 ЦР находятся в нулевом состоянии. В результате чего на выходе 1 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /эт4 = 1285о (см. гл. 1, рис. 1.28). Так как /отс - /эт4 = 1365б0 - 12850 = 123750 > 0, то на выходе 3 компаратора появляется 0. Состояния 1 на втором выходе ЦР и первом выходе КЛ сохранятся. С выхода ЦР 1 поступает на вход 2 УФ ИКМ. Следовательно, первый символ кода сегмента Л=1.

Третий такт. С выхода генератора передачи ГОпер на третий выход ЦР поступает 1, выходы 4 ...8 ЦР находятся в нулевом состоянии. В результате чего на выходе 2 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /эт6 = 51280 (см. гл. 1, рис. 1.28), а эталон /эт4 = 12880 отключается. Так как /отс - /эт6 = 136580 - 51250 = 85380 > 0, то на выходе 3 компаратора появляется 0. Состояния 1 на третьем выходе ЦР и на первом, втором выходах КЛ сохранятся. Эта 1 с выхода ЦР поступает на вход 3 УФ ИКМ. Второй символ кода сегмента К=1.

Четвертый такт. С выхода генератора передачи ГОпер на четвертый выход ЦР поступает 1, выходы 5...8 ЦР находятся в нулевом состоянии. В результате чего на выходе 3 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 комп"аратора подключается эталон /эт7 = 102480 (см. гл. 1, рис. 1.28), а эталон /„б = 51250 отключается. Так как /отс -/„6=13658„ - 1О248о = 34180 > 0, то на выходе 3 компаратора появляется 0. Состояния 1 на четвертом выходе ЦР и на третьем выходе КЛ сохранятся

Состояние 1 сохраняется только на одном из восьми выходов (эталонов), соответствующего нижней границе сегмента. Этот же эталон подключается и ко входу 2 компаратора К от ГЭТ\ и остается подключенным на все оставшееся время кодирования. С выхода ЦР 1 поступает на вход 4 УФ ИКМ. Третий символ кода сегмента 2=1. На этом завершается второй этап кодирования.

Таким образом, за четыре такта формируются: символ полярности отсчета равный Р = 1, и три символа кода сегмента Х= l,Y= I nZ= 1.

|

Третий этап кодирования - определение и кодирование номера уровня квантования сегмента, в пределах которого находится амплитуда отсчета /отс. Таких уровней квантования в пределах каждого сегмента 16, и все они могут быть получены с помощью дополнительных эталонных значений (см. табл. 1.8). Для рассматриваемого примера отсчет находится в в седьмом сегменте, для которого дополнительные эталонные значения равны /эт4 = 51280, /Этз = 25680, /ЭТ2 = 128бо и /ЭТ1 = 6450, а шаг квантования для этого сегмента равен 87 = 648о, где, напомним, 8о - шаг квантования нулевого (центрального) сегмента.

Пятый такт. С выхода генератора передачи ГОпер на пятый выход ЦР поступает 1, выходы 6...8 ЦР находятся в нулевом состоянии (2...4 -в состоянии 1). В результате чего на выходе 5 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /^ = 5128о. Сигнал на входе 2 компаратора равен /эт7 + /эт4 = Ю248о + 51280 = 15368V Так как /„„;-- (/эт7 + /эт4) = 136580 - 15368О = - 171б0 < 0, то на выходе 3 компаратора появляется 1. Состояния 1 на пятом выходе ЦР и на пятом выходе КЛ заменятся на 0. Эталон /эт4 = 51280 от входа 2 компаратора отключается. С выхода ЦР 0 поступает на вход 5 УФ ИКМ. Первый символ кода номера уровня квантования сегмента А = 0.

Шестой такт. С выхода генератора передачи ГОпер на шестой выход ЦР поступает 1, выходы 7...8 ЦР находятся в нулевом состоянии (2...4 -в состоянии 1, а 5 - 0). В результате чего на выходе 6 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /эт5 = 256&V Сигнал на входе 2 компаратора равен /ЭТ7 + /этз = Ю245О + 25б8о = 128О8о-Так как /отс - (/эт7 + /этз) = 136580 - 128О8о = 858о > 0, то на выходе 3 компаратора появляется 0. Состояние выходов ЦР не изменяется. С выхода ЦР 1 поступает на вход 6 УФ ИКМ. Следовательно, 2-й символ кода номера уровня квантования сегмента В=\.

Седьмой такт. С выхода генератора передачи ГОаер на седьмой выход

ЦР поступает 1, выход 8 ЦР находится в нулевом состоянии (2...4, 6 - в состоянии 1, а 5 - 0). В результате чего на выходе 7 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /эт4 = 12850. Сигнал на входе 2 компаратора равен /эт7 + /эт3 + /эт2 = 102450 + +256б0 +1285О = =140880. Так как /отс - (/эт7 + /эт. + /эт2) = 136550 - 140850 = - 438О < 0, то на выходе 3 компаратора появляется 1. Эта 1 устанавливает 0 на седьмом выходе ЦР, отключается /эт2 от входа 2 компаратора. С выхода ЦР 0 поступает на вход 7 УФ ИКМ. Следовательно, 3-й символ кода номера уровня квантования сегмента С = 0.

ЦР поступает 1, выход 8 ЦР находится в нулевом состоянии (2...4, 6 - в состоянии 1, а 5 - 0). В результате чего на выходе 7 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /эт4 = 12850. Сигнал на входе 2 компаратора равен /эт7 + /эт3 + /эт2 = 102450 + +256б0 +1285О = =140880. Так как /отс - (/эт7 + /эт. + /эт2) = 136550 - 140850 = - 438О < 0, то на выходе 3 компаратора появляется 1. Эта 1 устанавливает 0 на седьмом выходе ЦР, отключается /эт2 от входа 2 компаратора. С выхода ЦР 0 поступает на вход 7 УФ ИКМ. Следовательно, 3-й символ кода номера уровня квантования сегмента С = 0.

Восьмой такт. С выхода генератора передачи ГОпер на восьмой выход ЦР поступает 1, (2...4, 6 - в состоянии 1, а 5, 7 - 0). В результате чего на выходе 8 блока компрессорной логики КЛ появляется 1, которая управляет блоком коммутации эталонов БКЭ, и ко входу 2 компаратора подключается эталон /этз1= 648о. Сигнал на входе 2 компаратора равен /„7 + /этз + + /эт, = 1О248о + 25680 +6480 = 134450. Так как /Отс - (7эт7 + /эт3 + 1„0 = = 13658а ~ 13448о = 2180 > 0, то на выходе 3 компаратора появляется 0. Состояние символов на выходах ЦР и КЛ не изменяется. С выхода ЦР 1 поступает на вход 8 УФ ИКМ. Следовательно, 4-й символ кода номера уровня квантования сегмента D = 1.

Таким образом, за четыре такта формируются: символы кода номера уровня квантования отсчета 7-го сегмента: А = 0, В = 1, С = 0, D = I. Преобразователь кода ПК формирует выходной ИКМ сигнал в последовательном виде 11110101. Ошибка квантования при этом равна/эт7 = 136580--134480 = 2150, что не превышает половины шага квантования седьмого сегмента.

Процесс формирования ИКМ сигнала принято называть аналого-цифровым преобразованием. Обратное цифро-аналоговое преобразование или декодирование, осуществляется декодером. Декодер осуществляет цифро-аналоговое преобразование кодовой комбинации в отсчеты АИМ сигнала соответствующей амплитуды и полярности. Структурная схема нелинейного декодера приведена на рис. 2.14.

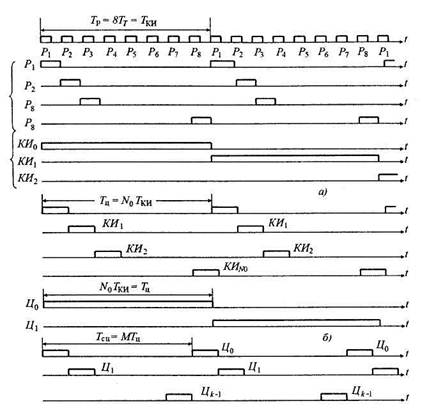

Декодер содержит цифровой регистр ЦР, блок экспандирующей логики ЭЛ, блок коммутации эталонов БКЭ и два генератора эталонных токов ГЭТ, и ГЭТ2 положительной и отрицательной полярности.

Принятый ИКМ сигнал, представляющий восьмиразрядную кодовую комбинацию, записывается в ЦР и в виде параллельного кода формируется на его выходах 1...8. Высший разряд, определяющий полярность отсчета, записывается на 8-м выходе, символы, определяющие код сегмента, записываются на 7, 6 и 5 выходах, символы кода номера уровня кванто-

Рис. 2.14. Структурная схема нелинейного декодера

вания записываются на 4, 3, 2 и 1 выходах ЦР. В соответствии с принятой кодовой комбинацией осуществляется включение эталонных токов. Их суммарная величина и определяет амплитуду принимаемого отсчета. Необходимо отметить, что для уменьшения погрешности преобразования уровни квантования декодера смещены на половину шага квантования по отношению к уровням кодера. Для этого в БКЭ добавлен еще один, 12-й корректирующий эталон, равный 0,5 шага квантования соответствующего сегмента.

Рассмотрим пример декодирования ранее полученной кодовой комбинации 11110101. Эта кодовая комбинация записывается в ЦР. Символ на восьмом выходе ЦР определяет полярность отсчета. Так как на восьмом выходе ЦР появилась 1, то через блок коммутации эталонов БКЭ осуществляется подключение положительных эталонов ГЭТ\. Так как на пятом-седьмом выходах ЦР записаны 1, то БКЭ во взаимодействии с блоком экспандерной логики ЭЛ подключают к ГЭТ\ эталон, соответствующий нижней границе сегмента, равный /эт10 = 102480. Так как на четвертом выходе ЦР записан 0, то следующий эталон ГЭТ, не будет подключен, Далее следует, что на третьем выходе ЦР записана 1, следовательно, к выходу ГЭТ, будет подключен эталон /„8 = 25680. В результате на выходе ГЭТ, формируется ток 1„ = 1„10 + /эт8 =Ю2480 + 256б0 = 12808,,. Если на втором

выходе ЦР записан 0, то следующий эталон пропускается. Если на первом выходе ЦР записана 1, то следующий эталон равный 1эт6 = 6480, подключается к выходу декодера и амплитуда суммарного тока на выходе декодера будет равна /эт = /этю + /эт8 + /ЭТ6 = Ю2450 + 2568О + 6450 = 134480.

Для снижения шумов квантования, как отмечалось выше, при декодировании используется еще 12-й корректирующий эталон, равный половине шага квантования соответствующего сегмента 5 се,, т.е. /к = 0,55 сег- Для приведенного примера шаг квантования седьмого сегмента равен 648О, следовательно, общее суммарное значение тока АИМ сигнала на выходе кодера будет равно /эт = /эт10 + /эт8 +1^+ /к = 102480 + 25680 + 6480 + 3280=137880.

На вход кодера поступил отсчет с амплитудой /отс = 13658о, сигнал на выходе декодера равен /эт = 137880, следовательно, искажения при кодировании-декодировании равны /иск = /отс - /эт = 13658о -13788о = — 135о, что по абсолютной величине не превышает половины шага квантования.

2.4. Генераторное оборудование цифровых систем передачи 2.4.1. Общие принципы построениягенераторного оборудования

Для работы функциональных блоков ЦСП с временным разделением каналов на всех этапах цифровой обработки сигналов, мультиплексирования и демультиплексирования цифровых потоков, формирования линейного цифрового сигнала, обеспечения синхронной работы оконечного оборудования требуются определенного вида управляющие сигналы, параметры которых строго регламентированы во времени. Формирование управляющих сигналов осуществляется генераторным оборудованием (ГО), которое выполняется отдельно для передающей ГОпер и приемной ГО„Р частей оконечных станций.

Генераторное оборудование обеспечивает формирование и распределение импульсных последовательностей, управляющих процессами дискретизации, кодирования-декодирования, временного группообразования, ввода-вывода символов служебных сигналов на определенные позиции цикла передачи и т. д. От ГО необходимо получить импульсные последовательности со следующими основными частотами:

- частотой дискретизации Fa (обычно равной 8 кГц);

- тактовой частотой первичного цифрового потока (ШДП), равной

где т - число элементов в кодовой комбинации, 7VKlf - число канальных интервалов ПЦП и равной

fT = Fam NKH = 8-8-32 = 2048 кГц;

- частотой следования кодовых комбинаций (канальных интервалов),

равной FKK = \1ТЮ = Fa NKll =fT I m;

- тактовыми частотами цифровых потоков более высокого порядка,

получаемыми в результате объединения определенного числа цифровых

потоков более низкого порядка.

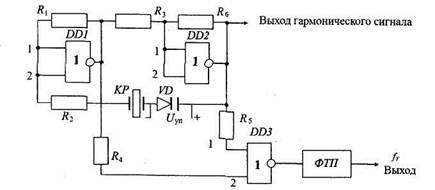

Рассмотрим построение ГО первичной цифровой системы, для которой необходимые импульсные последовательности можно получить путем деления тактовой частоты, получаемой от высокостабильного автономного задающего генератора ЗГ с относительной нестабильностью не хуже ± 10"6 (рис. 2.15). На выходе ЗГ формируется гармонический высокостабильный сигнал с частотой, обычно равной или кратной тактовой частоте/т. Формирователь тактовой последовательности ФТП вырабатывает основную последовательность импульсов с частотой следования/^ Импульсы тактовой последовательности используются при выполнении операций кодирования и декодирования, формирования и обработки линейного цифрового сигнала.

|

Делитель разрядный ДР формирует т импульсных последовательностей Pi, Рг...Рт. Число разрядных импульсов, формируемых ДР, равно числу разрядов кодовой комбинации, а частота их следования для т = 8 равна FK=fT/m = 2048 /8 = 256 кГц. Импульсные последовательности с выхода ДР используются для правильного определения каждого разряда кодовой комбинации, при выполнении операций кодирования и декодирования, а также при формировании группового ИКМ сигнала, когда необходимо выделить временные интервалы для передачи соответствующих позиций синхроимпульсов, сигналов управления и взаимодействия и различного вида сервисных сигналов.

Делитель канальный ДК формирует управляющие канальные импульсы последовательности КИд, КИ\...КИц-\- Частота следования КИ равна частоте дискретизации Fa.

Делитель цикловой ДЦ служит для формирования цикловых импульсных последовательностей Цо, Цх ...Цк-ь где k - число циклов в сверхцикле. Для к = 16 частота следования цикловых импульсов равна Fu = Fa/ к = = 8000/16 = 500 Гц.

Обычно предусматривается несколько режимов работы генераторного оборудования оконечных станций:

- внутренней синхронизации, при котором осуществляется работа от

местного высокостабильного автономного ЗГ (рис. 2.15)

— внешнего запуска, при котором осуществляется работа от внешнего

задающего генератора ВЗГ.

Рис. 2. 15. Структурная схема ГО передачи

- внешней синхронизации, при котором осуществляется подстройка частоты местного ЗГ с помощью фазовой автоматической подстройки частоты (ФАПЧ), управляемой внешним сигналом.

Наличие установочных входов обеспечивает (при необходимости) возможность подстройки ГО данной станции к работе ГО другой станции, выбранной за ведущую станцию. Как следует из рис. 2.15, формирование необходимых последовательностей импульсов реализуется делением частоты. Временные диаграммы работы ГО с использованием делителей частоты приведены на рис. 2.16. На вход делителя разрядных импульсов ДР от формирователя тактовой последовательности поступает периодическая последовательность импульсов. ДР формирует восемь разрядных импульсов Р\...Р%. Каждый разрядный импульс сдвинут относительно следующего на тактовый интервал. Интервал следования одноименных разрядных импульсов равен Тр= 8ТТ. На рис. 2.16,а показано положение импульсных последовательностей Р/...Р8 относительно тактовых. Из любой последовательности Pi формируются управляющие последовательности КИ0, КИ\, KHff.i, определяющие границы канальных интервалов и их временное положение. Расположение КИ относительно разрядных импульсов и тактовой последовательности также видно из рис. 2.16,д. На рис. 2.16,6 показано расположение импульсов управляющих последовательностей Цо и Ц/ относительно последовательностей КИо..-KHn-i, а на рис. 2.16,в - взаимное расположение циклов Z/o- • • Цы в сверхцикле.

Схема ГО приема отличается от схемы ГО передачи следующими особенностями, обеспечивающими работу ГО приема синхронно и синфазно с ГО передачей. Во-первых, импульсная последовательность с тактовой частотой fT будет поступать на вход ДР не от ЗГ, а от выделителя тактовой частоты - ВТЧ. Во-вторых, установка ГО приема по циклу и по сверхциклу осуществляется с помощью сигналов, поступающих от приемника синхросигнала, о чем будет сказано ниже.

Рис. 2.16. Временные диаграммы работы генераторного оборудования

2.4.2. Задающие генераторы

Основным требованием, предъявляемым к задающим генераторам (ЗГ) ЦСП, является стабильность частоты. В то же время они должны иметь возможность перестройки частоты в определенных пределах. Выполнение противоречивых требований обеспечения стабильности частоты ЗГ (в режиме автогенерации) и реализации определенной перестройки учитывается при выборе соответствующей схемы ЗГ. Относительная нестабильность частоты ЗГ должна быть не выше 10~5, и поэтому в схемах ЗГ для стабилизации частоты используются кварцевые резонаторы (КР). Частота

Рис. 2.17. Принципиальная схема ЗГ на транзисторах

ЗГ выбирается в целое число большей, чем тактовая частота/т. Так, например, ЗГ аппаратуры формирования первичного цифрового потока типа ИКМ-30 вырабатывает гармоническое колебание с частотой/зг= 8192 кГц. Выбор частоты генерации, в 4 раза превышающей тактовую частоту потока, позволяет осуществить почти оптимальное построение ЗГ. В схему ЗГ входят делитель частоты (ДЧ) и формирователь тактовой последовательности (ФТП). В настоящее время ЗГ цифровых систем передачи реализуются как на дискретных (рис. 2.17), так и на логических элементах (рис. 2.18).

Рис. 2.18. Функциональная схема ЗГ на логических элементах

Схема ЗГ (рис. 2.17) представляет двухкаскадный усилитель с положительной обратной связью, в состав которого входит кварцевый резонатор КР. Режим по постоянному току первого каскада обеспечивается резисторами Л1...Л4, второго - резисторами R5...R6. Для изменения частоты ЗГ в заданных пределах включен варикап VD, управляемый напряжением Uyn, которое может изменяться или регулироваться устройством фазовой автоподстройки частоты при работе ЗГъ режиме внешней синхронизации.

Схема ЗГ (рис. 2.18) состоит из трех инверторов DDI...DD3, сопротивлений R/ и /?5 обеспечивают перевод элементов D\ и D2 в активный режим. Длительность импульсов можно менять подборкой резисторов R\ и Re, сопротивления которых совместно с входной емкостью элемента DD3 образуют цепь временной задержки. Подстройка частоты осуществляется управляемым варикапом VD.

Учитывая, что ЗГ должен работать в режиме как автогенерации, так и внешнего управления частотой в схеме предусматривается возможность переключения режимов. На рис. 2.19 представлена схема задающего генератора, включающая в себя автогенератор с кварцевой стабилизацией, собственно ЗГ и схему фазовой автоподстройки частоты (ФАПЧ), состоящей из фазового детектора - ФД, фильтра нижних частот - ФНЧ и усилителя постоянного тока, формирующих сигнал управления перестройкой частоты ЗГ.

В режиме автогенерации устанавливаются перемычки 1 — 2, 4 - 6, а в режиме внешней подстройки частоты - перемычки 2-3, 4 ~ 6 и 7 - 8. При этом в работу включается схема ФАПЧ, которая сравнивает фазы внешней частоты синхронизации и собственной частоты ЗГ. Если имеют

Рис. 2.19. Схема ЗГ с фазовой автоподстройкой частоты

расхождения фаз этих частот, то вырабатывается соответствующий управляющий сигнал, и частота ЗГ подстраивается под частоту синхронизации.

В режиме использования внешнего генератора устанавливается перемычка 5-6. Работа схемы от местного генератора и работа от внешнего генератора совершенно одинаковы.

В режиме внешней синхронизации схема работает следующим образом: устанавливается перемычка 7-8; частота местного ЗГ и частота от внешнего генератора поступают на фазовый детектор ФД на выходе которого образуется разностный сигнал; ФНЧ выделяет постоянную составляющую этого сигнала, величина которой пропорциональна расхождению частот воздействующих на него сигналов; сигнал с выхода ФНЧ усиливается УПТ, на выходе которого формируется сигнал напряжением £/уп, управляющий перестройкой частоты ЗГ (воздействуя, к примеру, на варикап).

2.4.3. Делители частоты

Схемы делителей различного назначения (разрядных, канальных, циклов и сверхциклов) легко реализуются на основе счетчиков, регистров, дешифраторов и других логических схем.

Функциональная схема делителя разрядов ДР (для m = 8) с использованием трехразрядного двоичного счетчика на триггерах Тг{...Тг3 показана на рис. 2.20,а.

|

Реализовать такой ДР можно и применением кольцевого счетчика из восьми триггеров Тг\...Тг%, рис. 2.20,6. Аналогичным образом можно построить и другие делители. На практике более широкое распространение получил первый вариант, который для своей реализации требует меньшего числа триггеров

Рис. 2.20. Функциональные схемы делителей разрядов

Вопросы для самоконтроля

1. Назовите основные способы снижения затухания при дискретизации анало

говых сигналов.

2. В чем сущность резонансного способа дискретизации?

3. Процесс кодирования в кодерах последовательного счета. Достоинства и

недостатки кодеров последовательного счета.

4. Процесс кодирования в линейных кодерах поразрядного кодирования или

взвешивающего типа.

5. Назначение инверторов DDi и DD2 линейного кодера взвешивающего типа

для двухполярных сигналов. Назначение устройства формирования ИКМ сигнала.

6. Назначение компандерной логики в схеме нелинейного кодера.

7. Назначение экспандерной логики в схеме нелинейного декодера.

8. Изобразите структурную схему цифрового регистра или преобразователя

последовательного кода в параллельный.

9. На вход нелинейного кодера поступает АИМ-2 сигнал с амплитудой - 10188о

Определить структуру кодовой комбинации на выходе нелинейного кодера.

10. На вход нелинейного декодера поступает ИКМ сигнал вида 00111101 Оп

ределите амплитуду АИМ-2 отсчета на выходе нелинейного декодера.

11. Сформулируйте основные требования к генераторному оборудованию

ДСП.

12. Укажите назначение основных элементов структурной схемы генераторно

го оборудования ЦСП.

13. Поясните работу схемы задающего генератора, изображенного на рис. 2.16.

14. Поясните работу схемы задающего генератора, изображенного на рис. 2.17.

15. Разработайте функциональную схему ЗГ с использованием двух инверто

ров.

16. На примере схемы рис. 2.18 поясните режимы работы генераторного обо

рудования.

17. Попытайтесь изобразить временные диаграммы работы схемы в режиме

внешней синхронизации.

18 Изобразите функциональную схему ДК для формирования канальных последовательностей импульсов с использованием кольцевого счетчика.

19. Изобразите функциональную схему ДК для формирования канальных последовательностей импульсов с использованием соответствующего разрядного счетчика.