Архитектура NOR

Самая простая для понимания архитектура флэш-памяти — архитектура NOR (рис. 43).

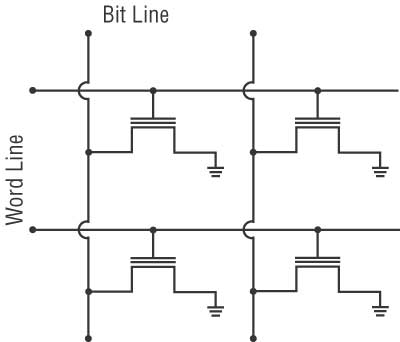

Рисунок 43 - Архитектура NOR

Как уже отмечалось, для инициализации ячейки памяти, то есть для получения доступа к содержимому ячейки, необходимо подать напряжение на управляющий затвор. Поэтому все управляющие затворы должны быть подсоединены к линии управления, называемой линией слов (Word Line). Анализ содержимого ячейки памяти производится по уровню сигнала на стоке транзистора. Поэтому стоки транзисторов подключаются к линии, называемой линией битов (Bit Line).

Своим названием архитектура NOR обязана логической операции ИЛИ-НЕ (английская аббревиатура — NOR). Логическая операция NOR над несколькими операндами дает единичное значение, когда все операнды равны нулю, и нулевое значение во всех остальных случаях. Если под операндами понимать значения ячеек памяти, то в рассмотренной архитектуре единичное значение на битовой линии будет наблюдаться только в том случае, когда значение всех ячеек, подключенных к данной битовой линии, равно нулю (все транзисторы закрыты).

Архитектура NOR обеспечивает произвольный быстрый доступ к памяти, однако процессы записи (используется метод инжекции горячих электронов) и стирания информации происходит достаточно медленно. Кроме того, в силу технологических особенностей производства микросхем флэш-памяти с архитектурой NOR, размер самой ячейки получается весьма большим и потому такая память плохо масштабируется.