Лекция 4. Элементы последовательной логики, триггеры.

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от их последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательностной логикой. Основным элементом последовательностной логики является триггерный элемент или просто триггер.

Триггером называется устройство, обладающее двумя состояниями устойчивого равновесия и способное под воздействием внешнего управляющего сигнала переходить скачком из одного состояния в другое.

Основные области применения триггера:

запоминающая ячейка в устройствах электронной памяти ЭВМ;

элемент деления на 2 в импульсных счетчиках и делителях частоты;

устройство для расширения (увеличения длительности) импульсов;

устройство, восстанавливающее форму прямоугольного импульса.

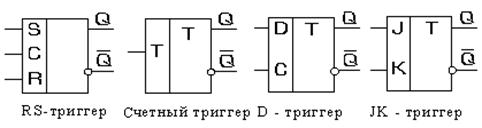

Классификация триггеров по способу организации логических связей:

триггеры с раздельным запуском или триггеры с установочными входами – RS-триггеры;

триггеры со счетным входом Т-триггеры;

Триггеры с приемом информации по одному входу – D-триггеры;

Универсальные триггеры – JK-триггеры.

По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация, записанная в триггер, может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация на выходе может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом.

Как правило, триггер имеет два выхода: прямой Q и инверсный  Состояние триггера определяется по прямому выходу Q. Число входов зависит от выполняемых функций:

Состояние триггера определяется по прямому выходу Q. Число входов зависит от выполняемых функций:

S – вход установки триггера в единичное состояние;

R – вход установки триггера в нулевое состояние;

Т – счетный вход;

D – вход приема информации;

С – вход синхронизации;

J,K – логические входы;

V – вход разрешения / запрета работы триггера.

Условные обозначения триггеров приведены на рис.4.1.

Рис.4.1. 6. Условные обозначения триггеров

Рис.4.2. . Схема асинхронного RS-триггера и его условное

обозначение (кружки у входов указывают на инверсные входы

– управление сигналом логического 0)

В основе всех схем триггеров лежит основной (базовый триггер защелка ) асинхронный RS-триггер. RS-триггер может быть построен на двух логических элементах И-НЕ (рис.4.2) (или ИЛИ-НЕ).

Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента.

Триггер имеет два входа: S – вход установки в единичное состояние (от англ. set – установка) и R – вход сброса в нулевое состояние (от англ. reset – сброс). Логика элементов И-НЕ, на которых построен триггер имеет простое словесное выражение: любой ноль на входе дает единицу на выходе. Из этого следует, что управляющими сигналами для этого триггера будут сигналы логического 0.

При подаче нуля на вход S и единицы на вход R (S=0, R=1) на прямом выходе будет уровень логической 1. Эта единица по цепи обратной связи поступает на один из входов нижнего по схеме элемента и вместе с единицей на входе R дает логический 0 на инверсном выходе. Это режим установки триггера в единичное состояние.

При входных сигналах S=1 и R=0 триггер будет установлен в нулевое состояние: на прямом выходе уровень логического 0, на инверсном – 1.

При подаче на оба входа нулевых сигналов на обоих выходах триггера появится уровень логической 1. Это запрещенный режим. Нельзя одновременно подавать сигналы на установку триггера в нулевое и единичное состояние.

В случае, если S=1 и R=1, то триггер не изменяет своего состояния. В этом можно убедиться, предполагая последовательно, что триггер находился в нулевом или единичном состоянии. Полная таблица истинности RS-триггера приведена в табл. 4.1.

Таблица 4.1. 4

| S | R |

|

|

|

Уравнения, описывающие эту таблицу для  и

и  после их упрощения (способы написания таких уравнений описаны ниже в разделе «Синтез цифровых схем») имеют вид:

после их упрощения (способы написания таких уравнений описаны ниже в разделе «Синтез цифровых схем») имеют вид:

и

и  . Здесь

. Здесь  - состояние триггера до подачи управляющих сигналов,

- состояние триггера до подачи управляющих сигналов,  - состояние триггера после подачи управляющих сигналов.

- состояние триггера после подачи управляющих сигналов.

При S=0 и R=0

при S=0 и R=1

при S=1 и R=0

при S=1 и R=1

Рис.4.3. 3 8. Схема синхронного RS-триггера на элементах И-НЕ

В синхронном RS-триггере (рис. 4.3 8) использованы 4 логических элемента И-НЕ.

Вход С – вход синхронизации. Переключение триггера под действием входных сигналов S и R возможно только при наличии синхронизирующего импульса, т.е. при С=1. При таком (единичном) сигнале на входе С входные элементы И-НЕ по другому входу выполняют функцию НЕ, т.е. этот триггер по входам S и R управляется единичными сигналами. При С=0 на выходах входных элементов будут уровни логической 1, что для следующего за входными элементами простого RS-триггера (см. табл.4.1) определяет режим хранения, т.е. триггер хранит свое предыдущее состояние и не переключается.

При С=1, S=0 и R=0 на выходах входных элементов уровни логической 1 – триггер находится в режиме хранения (см. рис.4.4).

При С=1, S=0 и R=1 на прямом выходе появится логический 0, на инверсном – 1. Это режим установки триггера в нулевое состояние.

Рис.4.4. 9. Распределение сигналов в синхронном RS-триггере при

разных комбинациях сигналов на входах R и S (при С=1)

При С=1, S=1 и R=0 на прямом выходе логическая 1, на инверсном – 0. Это режим установки триггера в единичное состояние.

При С=1, S=1 и R=1 на обоих выходах уровень логической 1 – запрещенный режим. Запрещено одновременно подавать сигналы на установку триггера в единичное и нулевое состояние.

Уравнения для синхронного RS-триггера:

Подставляя в уравнения разные значения С, S, R и Qt , получаем результаты, совпадающие с данными, полученными при анализе схемы.

D-триггер (рис. 4.5 10) имеет в своем составе 4 логических элемента И-НЕ, два из которых образуют простой RS-триггер, а входные подключены к клеммам D (вход приема информации) и С (вход синхронизации). При С=0, как и в синхронном триггере, на выходах входных элементов установятся уровни логической 1. Для выходного RS-триггера это режим хранения.

Рис. 4.5 10. Схема D-триггера на логических элементах И-НЕ

Независимо от состояния входа D на выходе информация не меняется (Qt+1=Qt). При С=1 информация со входа D переписывается на выход Q (Q t+1 = D t). Проследить за состояниями сигналов во всех точках схемы D-триггера при D=0 и D=1 можно по рис. 11.

Рис.4.6 11. Распределение сигналов в D-триггере при D=0 (слева) и

D=1 (справа)

В Т-триггере, при каждом импульсе на входе Т, триггер переключается в противоположное состояние. Т-триггер может быть построен на основе D-триггера при соединении инверсного выхода  со входом D. Вход С D-триггера становится входом Т Т-триггера. Т-триггер может быть построен также на основе синхронного RS-триггера соединением входа R с прямым выходом Q, а входа S с инверсным выходом

со входом D. Вход С D-триггера становится входом Т Т-триггера. Т-триггер может быть построен также на основе синхронного RS-триггера соединением входа R с прямым выходом Q, а входа S с инверсным выходом  (рис.4.7 12).

(рис.4.7 12).

Принцип работы Т-триггера иллюстрируется диаграммами напряжений на рис. 13.

Рис.4.7 12. Варианты реализации Т-триггера

Рис.4.8 13. Диаграммы напряжений для Т-триггера, построенного на

основе D-триггера (слева) и синхронного RS-триггера (справа)

Для реализации Т-триггера необходимо использовать не простые (статические) D или RS-триггеры, описанные выше и срабатывающие по единичному уровню на входе С, а динамические триггеры, срабатывающие по фронту сигнала на входе С. Тогда для схемы Т-триггера на основе D-триггера к моменту прихода первого фронта на входе С, на входе D был уровень логической 1. Эта единица и переписывается на выход Q согласно логике D-триггера. На инверсном выходе появится логический 0. К приходу второго фронта входного сигнала (С) на входе D был уровень логического 0. Он и перепишется на выход Q. Эти процессы записи информации со входа D на выход Q показаны на рис. 4.8 стрелками. Для Т- триггера на основе синхронного RS-триггера процессы аналогичны и основаны на логике синхронного RS-триггера. К моменту прихода первого фронта сигнала на вход С, на входе R был уровень логического 0, а на входе S – уровень логической 1. Триггер установится в единичное состояние. При следующем такте (фронте на входе С) входы R и S обменяются состояниями, на выходе Q появится уровень логического 0.

Таким образом, при каждом входном импульсе Т-триггер переключается в противоположное состояние. Если сравнить периоды входного и выходного сигналов, то можно заметить, что период выходного сигнала в 2 раза больше входного. Т.е. Т-триггер является делителем частоты на 2 и используется в схемах деления частоты и в цифровых счетчиках.

Триггер Шмидта

Триггер Шмидта применяется для формирования входного сигнала произвольной формы в сигналы, принимающие два стандартных уровня ”0” и “1”. Варианты схем таких формирователей показаны на рис. 4.9

рис 4.9

На рис. 4.9, а показана схема триггера Шмитта, в которой применены два инвертора, входящие в серию логических транзисторно-транзисторных интегральных схем. Положительная обратная связь между инверторами обеспечивается за счет резистора R1, включенного в общую цепь питания элементов. Для увеличения влияния цепи обратной связи, ток через второй инвертор увеличен путем включения дополнительного резистора R2 между выходом Э2 и источником питания. Подобный формирователь на интегральных схемах серии К1533 удовлетворительно работает до частоты несколько мегагерц при подаче на вход синусоидального напряжения амплитудой 0,5 - 0,8 В.

В триггерах Шмитта положительную обратную связь можно ввести также путем включения резистора между выходом второго инвертора и входом первого (рис. 4.6, б). Входное напряжение в этом формирователе подается через дополнительный резистор R1, сопротивление которого также влияет на глубину положительной обратной связи. Увеличение сопротивления этого резистора увеличивает коэффициент положительной обратной связи и уменьшает чувствительность формирователя к входному напряжению.

Вопросы по теме

1. Классификация триггеров простейший триггер защелка RS-триггеры

2. синхронные и асинхронные триггеры.

3. Т-триггеры и D-триггеры.

4. Универсальные триггеры – JK-триггеры

5. триггер Шмидта