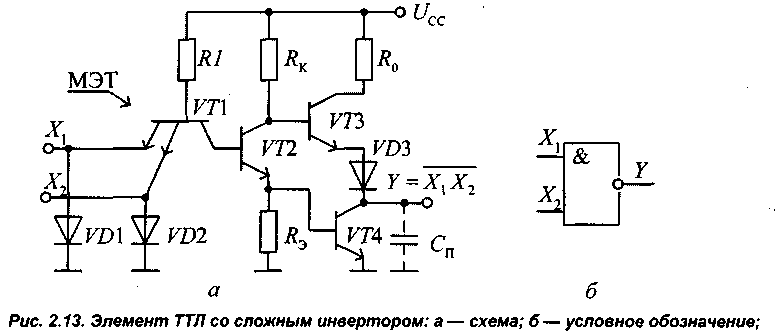

Транзисторно-транзисторный логический элемент со сложным инвертором

В микросхемах ТТЛ используют сложные инверторы, которые повышают быстродействие и нагрузочную способность элементов. Схема базового (типового) элемента ТТЛ со сложным инвертором содержит три основных каскада (рис. 4.24, а):

1. Входной каскад, реализующий операцию И (транзистор VT1, резистор R1). Ко всем входам МЭТ подключены демпфирующие (антизвонные) диоды, ограничивающие влияние импульсов помех отрицательной полярности.

2. Фазоинверсный каскад (транзистор VT2, резисторы Rк и Rэ), управляющий выходными транзисторами с помощью противофазных изменений напряжений на коллекторе и эмиттере VT2.

3. Выходной двухканальный усилитель (транзисторы VT3, VT4, смещающий диод VD3, резистор R0). Сложный инвертор образуется совместной работой фазоинверсного и выходного каскадов.

Рисунок 4.24- Элемент ТТЛ со сложным инвертором: а -схема; б –усл. обозначение

При совпадении на входах элементов высоких уровней напряжений МЭТ переключается в инверсный режим и своим коллекторным током открывает транзистор VT2. Часть эмиттерного тока транзистора VT2 втекает в базу транзистора VT4 и открывает его. После быстрого разряда паразитной емкости Сп через коллектор насыщенного транзистора VT4 на выходе устанавливается низкий уровень напряжения. При этом транзистор VT3 — закрытый, поскольку напряжение, прикладываемое к последовательно включенным переходам базы и диода VD3, недостаточно для его открывания.

При подаче на один из входов напряжения низкого уровня МЭТ переключается в режим насыщения, ток его коллектора равен нулю, вследствие чего закрываются транзисторы VT2 и VT4. При этом открытый транзистор VT3 работает в режиме эмиттерного повторителя: на его вход поступает высокий уровень напряжения с коллектора закрытого транзистора VT2, а нагрузкой служит сопротивление закрытого транзистора VT2. Эмиттерный повторитель передает на выход высокое напряжение

U0H = UCC - 2U*

где 2U*— прямое падение напряжения на двух последовательно включенных переходах -базы транзистора VT5 и диода VD3.

Повторитель создает в нагрузке ток, в 50-100 раз превышающий его входное значение. Это также обеспечивает быстрый заряд паразитной емкости Сп.

В процессе переключения имеется кратковременный интервал, когда транзистор VT4 уже открыт, a VT3 — еще не успел закрыться. При этом возникает значительный импульс тока от источника питания на землю (сквозной ток). Для уменьшения амплитуды сквозного тока в коллекторе транзистора VT3 поставлен ограничительный резистор Ro = 100...200 Ом.

Рассмотренная схема элемента ТТЛ со сложным инвертором является типовой для ТТЛ серий К131, К133, К155 и др.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Какую систему элементов, в основном используют в компьютерной схемотехнике, и какие её особенности?

2. Какие виды логики у потенциальных элементов.

3. Расскажите о работе элемента ИЛИ диодного логического элемента.

4. Расскажите о работе элемента И диодного логического элемента.

5. Расскажите о работе элемента НЕ.

6. Расскажите о работе элемента НЕ-ИЛИ диодно-транзисторного логического элемента.

7. Расскажите о работе элемента НЕ-И диодно-транзисторного логического элемента

8. Расскажите об общих характеристиках ТТЛ логических элементов.

9. Расскажите о работе ТТЛ элемента с простым инвертором.

10. Расскажите о работе ТТЛ элемента со сложным инвертором.

| 4.3 Асинхронные и синхронные RS-триггеры |

4.3.1 Определение и назначение триггеров

4.3.2 Классификация триггеров

4.3.3 Динамические параметры и таблицы переходов

4.3.4 Асинхронные RS-триггеры

4.3.5 Синхронные RS-триггеры

Используемая литература: Н.П.Бабич, И.А.Жуков Компьютерная Схемотехника. Методы построения и проектирования: Учебное пособие. - «МК-Пресс» Киев, 2004. 576 с.

4.3.1 Определение и назначение триггеров

Триггер — это запоминающий элемент с двумя устойчивыми состояниями, изменение которых происходит под действием входных сигналов.

Как элемент компьютера, триггер предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1.

Схема триггера обеспечивает запись, считывание, стирание и индикацию хранимой двоичной информации.

На основе триггеров строят типовые функциональные узлы компьютеров — регистры, счетчики, накапливающие сумматоры, а также микропрограммные автоматы.

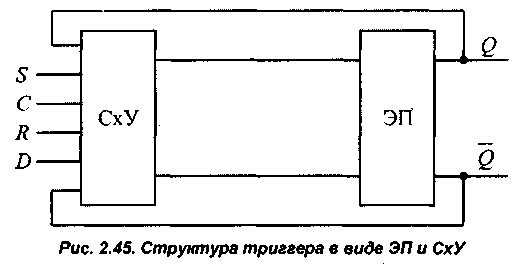

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и схему управления (СхУ), которая образует входную логику (рис. 4.25).

Состояние триггера определяется сигналами на прямом Q и инверсном  выходах.

выходах.

При положительном кодировании информации высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние Q = 1), а низкий уровень — значение лог. О (состояние Q = 0).

Рисунок 4.25 – Структура триггеров виде ЭП и СхУ

Изменение состояния триггера (его переключение) обеспечивается внешними сигналами и сигналами обратной связи на выходе триггера, поступающие на входы СхУ.

Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, Т, С, V и др..

В простейших схемах триггеров отдельная СхУ может отсутствовать.

Поскольку функциональные свойства триггеров определяются их СхУ, то названия основных входов переносятся на всю схему триггера.

4.3.2 Классификация триггеров

Триггеры классифицируют по следующим признакам:

• логике функционирования (RS, JK, D, Т и др.);

• способу записи информации (асинхронные и синхронные);

• моменту реакции на тактовый сигнал (статические, динамические);

• количеству тактов синхронизации (одно-, двух- и трехтактные);

• количеству ступеней (одно- или двухступенчатые триггеры);

• составу логических элементов (триггеры на элементах НЕ-И, НЕ-ИЛИ, НЕ-И-ИЛИ и др.).

В соответствии с логикой функционирования различают следующие триггеры:

• с раздельной установкой состояний "О" и "1" (RS-триггеры);

• с одним информационным входом (D-триггеры);

• со счетным входом (Т-триггеры);

• универсальные с раздельной установкой состояний "О" и "1" (JK-триггеры);

• комбинированные (RST-, RSJK-триггеры);

• со сложной входной логикой.

Входы триггеров разделяются на информационные (R, S, Т и др.) и управляющие (С, V).

Информационные (логические) входы предназначены для приема сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера.

Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов: синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход) и разрешающий сигнал V, поступающий на V-вход.

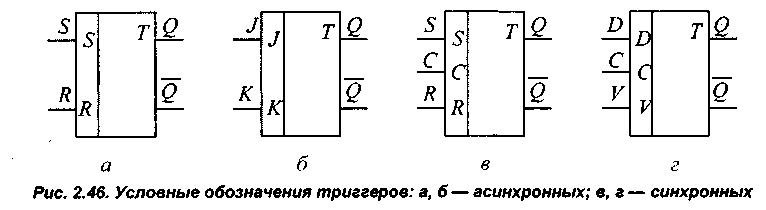

По способу записи (приема) информации различают асинхронные и синхронные (тактируемые) триггеры.

Триггеры, не имеющие С-входа, называются асинхронными (рис. 4.26, а и б).

В асинхронных триггерах запись информации производится в любой момент времени при поступлении сигналов на информационные входы.

Триггеры, имеющие С-вход, называются синхронными (рис. 4.26, в и г)..

В синхронном триггере запись информации возможна при совпадении сигналов на информационном и синхронном входах. Этим объясняется более высокая помехоустойчивость синхронных триггеров в сравнении с асинхронными.

Рисунок 4.26-Условные обозначения триггеров: а,б –асинхронные; в, г -синхронные

На V-входы триггера поступают сигналы, которые разрешают (V = 1) или запрещают (V = 0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на информационном, С- и V- входах.

В зависимости от количества тактовых сигналов, необходимых для формирования нового состояния, различают однотактные, двухтактные и многотактные триггеры.

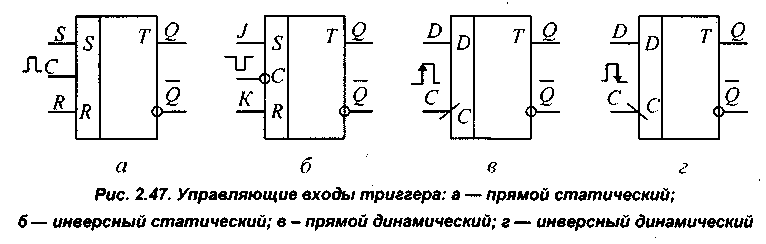

По способу управления записью (моменту реакции на тактовый сигнал) выделяют синхронные триггеры со статическим (по уровню), динамическим (по фронтам) и двухступенчатым управлением.

В асинхронных триггерах запись нуля и единицы возможна в любой момент времени, при этом входной информационный сигнал одновременно является и управляющим.

В синхронных триггерах с управлением по уровню запись информации возможна только в течение длительности тактового сигнала. При этом тактовые сигналы могут быть прямыми (изменяться от нуля к единице) или инверсными (изменяться от единицы к нулю) (рис. 4.27, а и б).

Рисунок 4.26-Управляющие входы триггеров: а -прямой статический;

б –инверсный статический; в –прямой динамический; г –инверсный динамический

При управлении фронтами разрешение на запись информации дается только в момент перепада тактового сигнала от нуля к единице (прямой динамический вход) или от единицы к нулю (инверсный динамический вход).

В другие моменты времени триггер не реагирует на входные информационные сигналы независимо от уровня тактового импульса (рис. 4.26, в и г).

4.3.3 Динамические параметры и таблицы переходов

Динамические параметры

Для триггеров установлены следующие динамические параметры, измеряемые на уровне половины амплитуды сигналов (рис. 4.27):

•  минимальная длительность импульса tc на тактовом входе;

минимальная длительность импульса tc на тактовом входе;

• минимальное время предварительной установки сигнала на информационном входе tycт;

• время восстановления (фиксации) tвос — минимальное время между нарастанием синхросигнала С и спадом информационного сигнала D; для асинхронных триггеров tвос — просто длительность входного сигнала;

• время переключения триггера tп.т — временной интервал между

Рисунок 4.27- Временные фронтом входного переключающего сигнала и фронтом сигнала

интервалы на выходе Q или  .

.

Минимальная длительность синхросигнала на входе триггера определяется максимальным временем переключения триггера tc ≥ tп.т max.

В двухступенчатом триггере с однотактной синхронизацией время переключения второй ступени определяется по отношению к спаду синхроимпульса.

Таблица переходов и логические уравнения RS-триггера

RS-триггером называют запоминающий элемент с раздельными информационными входами для установки его в состояние "0" (R-вход) и в состояние "1" (S-вход).

Название "RS-триггер" образовано от первых букв слов RESET (сброс) и SET (установка).

В таблице переходов RS-триггера (табл. 4.6) приняты обозначения:

• Rt, St, Qt, -значения логических переменных в момент времени t на входах R, S и выходе Q;

• Qt+1 — состояние триггера после переключения;

• К6, К7 — запрещенная комбинация сигналов (неопределенные коэффициенты на тех набо-

рах, где входные сигналы R, и S, одновременно принимают значение единицы).

Табл. 4.6

Табл. 4.6

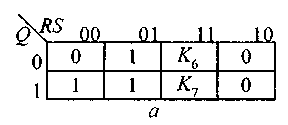

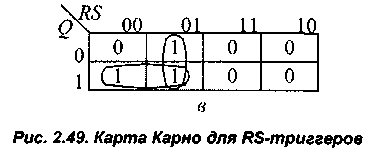

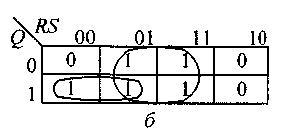

Рисунок 4.28-Карты Карно для RS-триггера

Таблице переходов соответствует карта Карно (рис. 4.28, а), где значения функции Qt+1 для минтермов Rt, St, Qt и Rt, St, Qt, заменены неопределенными коэффициентами К6 и К7.

Предположив, что комбинации входных сигналов Rt, St = 1 не существует, получим карты Карно для К6 = К7 = 1 (рис. 4.28, б) и К6 = К7 = 0 (рис. 4.28, в).

Из карт Карно получаем логические уравнения асинхронного RS-триггера:

К6 = К7 = 1 , Qt+1 = St  Qt (4.1)

Qt (4.1)

К6 = К7 = 0, Qt+1 =  (St

(St  Qt ). (4.2)

Qt ). (4.2)

Логические выражения (4.1) и (4.2) определяют новое состояние триггера Qt+1 в зависимости от старого состояния Qt и входных сигналов Rt и St.

В дальнейшем для простоты индекс t в правой части логического выражения опускается.

4.3.4 Асинхронные RS-триггеры