Устройство управления

Структура УУ определяется важнейшей характеристикой процессора – адресностью машинных команд. Рассмотрим структуру УУ для двухадресных команд и взаимодействие его элементов в процессе функционирования:

УВв, УВыв, внешняя память, АЛУ

Блок центрального управлениягенерирует сигнал о начале выполнения очередной команды (связь 1). Ее адрес А находится в счетчике адреса команд.

Блок выборки из памятипо сигналу считывает из ОЗУпо адресу А, который выбирается из счетчика адреса команд (связь 8), очередную команду (связь 2) и помещает ее на временное хранение в регистр команд(связь 3).

Дешифратор кода операциивыбирает код (связь 4) и расшифровывает его. Затем передает информацию блоку формирования управляющих сигналов(связь 10):

· если операция арифметическая, от блока формирования управляющих сигналовпоступает сигнал в блок выборки из памяти(связь 5) с командой считать из ОЗУ операнды, расположенные по адресам, указанным в регистрах первого и второго операндов(связь 6), и поместить их в соответствующие регистры АЛУ (о структуре АЛУ см. в п. 9.3). Затем формируется сигнал в АЛУна выполнение нужной операции (связь 7). Счетчик адреса команд увеличивается на объем команды (связь 9);

· если операция ввода-вывода, блок формирования управляющих сигналовформирует сигнал УВв и УВыв (связь 7). Счетчик адреса увеличивается на объем команды (по связи 9);

· если операция условного перехода, блок центрального управленияанализирует результат предыдущей операции, находящийся в АЛУ. Если знак результата отрицателен, в счетчик адреса командзаписывается адрес из регистра первого операнда. Если знак положителен, в счетчик адреса командзаписывается адрес из регистра второго операнда.Если результат равен 0, в счетчик адреса команддобавляется 1 (эти связи не показаны). Так реализуется принцип условного перехода.

· если операция безусловного перехода, в счетчик адреса командпересылается содержимое регистра первого операнда(связь не показана).

Арифметико-логическое устройство

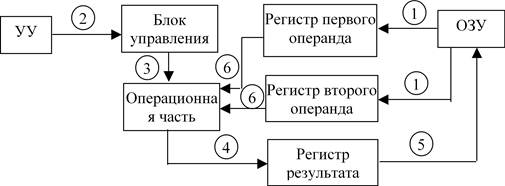

Структура АЛУ представлена на рисунке.

Исходные данные (операнды) по командам УУ (см выше) считываются из ОЗУ в регистры первого и второго операндов (связь 1).

Из УУ в блок управления АЛУ поступает команда на выполнение той или иной операции (связь 2), которая передается им в операционную часть (связь 3).

В соответствии с этой командой операционная часть выполняет нужное действие с данными, которые выбираются из регистров первого и второго операндов (связь 6). Результат заносится в регистр результата (связь 4), откуда – в ОЗУ (связь 5).

Структура регистров АЛУ, куда помещаются исходные и результирующие данные, а также размер регистров (число двоичных разрядов t) формируют понятие разрядной сетки (далее – сетки), которое используется ниже.