Основные особенности процессоров семейства TMS320 платформы С5000.

Высокая производительность процессоров этого семейства стала возможной благодаря специально разработанной архитектуре, позволяющей ускорить выполнение наиболее широко применяемых в цифровой обработке

операций. Следующие особенности архитектуры ядра С54х позволили существенно повысить производительность:

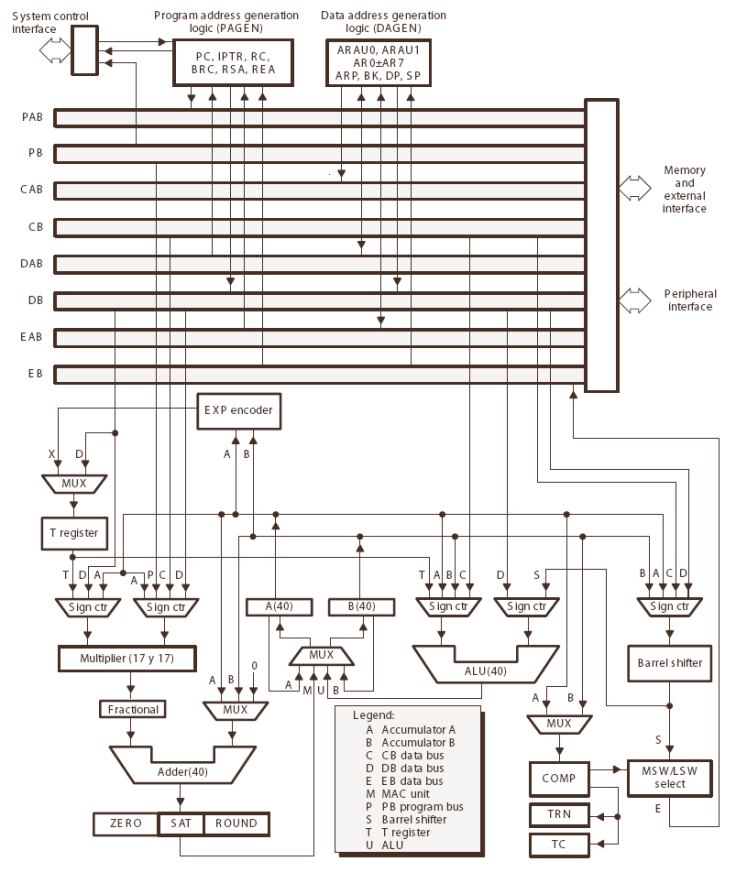

• четыре внутренние шины и два генератора адреса позволяют параллельно выполнять операции с несколькими операндами и снижают критические параметры доступа к памяти;

• 40-разрядный сумматор и два 40-разрядных аккумулятора позволяют производить параллельную обработку инструкций в одном цикле команды;

• второй дополнительный 40-разрядный аккумулятор на выходе умножителя позволяет выполнять неконвейерные МАС операции типа двух суммирований и умножения параллельно;

• одноцикловая нормализация и экспоненциальное декодирование дают поддержку операций с плавающей точкой, которые часто используются при кодировании речи;

• включенный в состав ядра Витерби-ускоритель сокращает выполнение операции «бабочка», применяемой, например, при декодировании канала GSM, до 4-х команд процессора;

• умножитель 17х17 разрядов позволяет выполнять 16-разрядное знаковое и беззнаковое умножение с округлением и контролем насыщения в одном командном цикле;

• 40-разрядное АЛУ может работать в режиме, когда выполняются одновременно две операции с 16-разрядными числами;

• восемь дополнительных регистров и программный стек позволяют применить наиболее развитый и эффективный С-компилятор.

Дальнейшим развитием успеха семейства процессоров С54х стало появление процессоров семейства С55х с новыми возможностями, позволяющими разработчику создавать широкий спектр средств от портативного Интернета до высокоскоростных беспроводных устройств, обеспечивая при этом минимальное на сегодняшний день энергопотребление 0,05 мВт на MIPS.

Существенно повысить производительность (до 140-800 MIPS или MMACS) и снизить энергопотребление позволяют следующие особенности архитектуры С55х:

• наличие в ядре процессора устройства автоматического управления питанием для всей периферии, памяти и отдельных устройств ЦПС, позволяющих отключать свободный домен;

• применение команд различной длины (от 8 до 48 бит) позволяет увеличить плотность кода и повысить эффективность использование каждого командного цикла, при этом длина выборки увеличена с 16 до 32 бит;

• сдвоенные 17х17-битные умножители с накоплением (МАС), второе 16-битное АЛУ, четыре регистра данных для выполнения простейших вычислений и четыре 40-разрядных аккумулятора позволяют параллельно выполнить значительно больше операций при более низком энергопотреблении.

2. Операционное устройство процессоров семейства TMS320С5х.

Операционное устройство включает в себя следующие основные блоки :

- арифметическо-логическое устройство;

- два аккумулятора;

- аппаратный умножитель;

- сдвигатель;

- блок сравнения, выбора и записи.