Двухступенчатые триггеры со статическим управлением

Особенность работы двухступенчатых триггеров заключается в том, что запись информации в первую ступень триггера производится при поступлении единичного значения сигнала на вход С, а перезапись во вторую ступень осуществляется по окончании действия управляющего сигнала на входе С (С=0). В одноступенчатых синхронных триггерах со статическим управлением, рассмотренных выше, подготовка записываемой информации должна осуществляться до прихода управляющего сигнала на вход С. В двухступенчатых триггерах смена входной информации может происходить и во время действия управляющего сигнала, так как перезапись информации из первой ступени во вторую происходит по окончании его действия. Следовательно, в двухступенчатых триггерах входная и выходная ступени тактируются «антисинхронно». Следствие этого – отсутствие режима прозрачности триггера при любом уровне синхросигнала. Это позволяет реализовать любые типы триггеров, свободные от режимов генерации, и дает возможность построения синхронных цифровых автоматов без опасных временных состязаний.

Двухступенчатые триггеры строятся несколькими способами:

– с разнополярным управлением;

– с инвертором;

– с запрещающими связями.

В первом варианте антисинхронное тактирование обеспечивается тем, что триггер первой ступени имеет прямой статический вход С, а триггер второй ступени – инверсный.

Во втором варианте ступени одинаковы по типу входа синхронизации С, а для их антисинхронного управления в цепь тактовых сигналов включен инвертор (рисунок 14, б).

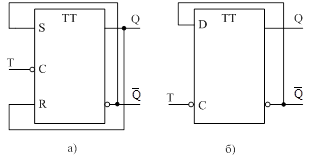

Рисунок 14 – Двухступенчатый RS-триггер со статическим управлением. Условное графическое обозначение (а) и упрощенная логическая схема (б)

В такой схеме возможны временные состязания сигналов: входной триггер состязается с инвертором. Если триггер переключится быстрее инвертора, то его новое состояние может успеть «проскочить» в выходной триггер, так как инвертор не успеет заблокировать входы этого триггера. Несмотря на это, вариант с инвертором находит широкое применение, при его проектировании просто заботятся об обеспечении нужного соотношения задержек инвертора и входного триггера.

Следует помнить, что разрешающим уровнем сигнала синхронизации считается тот, который переписывает информацию из входной ступени в выходную, так как именно при этом новая информация появляется на выходе триггера. Поэтому на рисунке 14, а вход С инверсный статический.

В третьем варианте сигналы блокировки второй ступени берутся со входов внутреннего асинхронного RS-триггера первой ступени.

Необходимо отметить, что в схеме на рисунке 14, как и в схеме одноступенчатого синхронного RS-триггера (10), одновременная подача единичных сигналов на входы S, R, C вызывает неопределенное состояние триггера. Этот недостаток устранен в схеме JK-триггера.

JK-триггер. УГО и логическая схема JK-триггера приведены на рисунке 15.

Рисунок 15 – Двухступенчатый JK-триггер со статическим управлением. Условное графическое обозначение (а) и упрощенная логическая схема (б)

Отличие в построении схемы JK-триггера от RS-триггера (рисунок 14) заключается во введении обратных связей с выходов триггера на его входы. В одноступенчатых RS-триггерах со статическим управлением (рисунок 10) обратные связи ведут к опасности появления в схеме режима генерации. Например, при С=1, триггеру, находящемуся в состоянии Q, разрешен прием состояния  и он переключается. После этого, если значение сигнала С остается единичным, то повторяется та же ситуация – триггер примет состояние Q и вновь переключится. Таким образом, пока С=1, схема ведет себя как генератор. Для исключения режима генерации в триггерах с обратными связями (JK-триггер и Т-триггер) применяют непрозрачные триггеры (двухступенчатые со статическим управлением или с динамическим управлением).

и он переключается. После этого, если значение сигнала С остается единичным, то повторяется та же ситуация – триггер примет состояние Q и вновь переключится. Таким образом, пока С=1, схема ведет себя как генератор. Для исключения режима генерации в триггерах с обратными связями (JK-триггер и Т-триггер) применяют непрозрачные триггеры (двухступенчатые со статическим управлением или с динамическим управлением).

Работа JK-триггера (рисунок 15) описывается таблицей состояний (таблица 6).

Таблица 6 – Таблица состояний двухступенчатого JK-триггера со статическим управлением

| Входы | Выход | Режим работы | ||||

|

| C | J | K | Qt+1 | |

| X | X | Предустановка (асинхронный сброс) | ||||

| X | X | Qt | Хранение | |||

| Qt | Хранение | |||||

| Загрузка 0 | ||||||

| Загрузка 1 | ||||||

| Счетный |

Из таблицы состояний следует, что для первых трех комбинаций сигналов на входах J, K, C JK-триггер работает как синхронный RS-триггер (таблица 4). При четвертой комбинации входных сигналов J = K = C = 1 JK-триггер переходит в счетный режим благодаря обратным связям. В этом случае каждый тактовый импульс на входе С меняет состояние триггера на противоположное  Тем самым выполняется логическая функция «Сложение по модулю два» предыдущего состояния триггера Qt и единичного сигнала на входе С, т.е. JK-триггер выполняет функцию Т-триггера.

Тем самым выполняется логическая функция «Сложение по модулю два» предыдущего состояния триггера Qt и единичного сигнала на входе С, т.е. JK-триггер выполняет функцию Т-триггера.

JK-триггер является универсальным. На его основе в зависимости от способа использования входов можно реализовать схемы двухступенчатых RS-, T-, D-триггеров. На рисунке 16 представлены различные варианты включения универсального JK-триггера.

Рисунок 16 – Схема использования JK-триггера в качестве RS-триггера (а), синхронного Т-триггера (б), асинхронного Т-триггера (в) и D-триггера (г)

T-триггер. Как отмечалось выше, этот триггер реализует логическую функцию «Сложение по модулю два». С приходом каждого импульса на счетный вход Т состояние триггера меняется на противоположное, что соответствует арифметическому сложению без учета единицы переноса. Т-триггер может быть построен на базе двухступенчатых синхронных RS-, D- или JK-триггеров. На рисунке 17 представлен Т-триггер на основе RS- и D-триггеров. Реализация Т-триггера на основе JK-триггера показана на рисунке 16, б и в.

Рисунок 17 – Схема реализации Т-триггера на основе двухступенчатого RS-триггера (а) и на основе D-триггера (б)

Представленный на рисунке 16, б синхронный Т-триггер на основе JK-триггера может работать в двух режимах – счетном и хранения (таблица 6). Эти режимы обеспечиваются подачей на вход Т единичного и нулевого сигналов соответственно и аналогичны режимам JK-триггера.

Работа Т-триггера поясняется таблицей состояний (таблица 7) и временными диаграммами (рисунок 18).

Таблица 7 – Таблица состояний Т-триггера

| Логические аргументы | Логическая функция | Режим работы | ||||||

| T | Qt | Qt+1 | ||||||

| Хранение 0 | ||||||||

| Хранение 1 | ||||||||

| Счетный | ||||||||

| Счетный | ||||||||

Рисунок 18 – Временные диаграммы работы Т-триггера

Из временных диаграмм следует, что Т-триггер делит частоту входных импульсов на два, т.е. Т-триггер является основой для построения делителей частоты импульсов.

По данным таблицы 7 можно записать характеристическое уравнение Т-триггера в СДНФ:

. (9)

. (9)

Из логической функции (9) следует, что Т-триггер действительно выполняет логическую функцию «Сложение по модулю два».